# Controlled Impedance Test

### by MARTYN GAUDION

he increasing requirement for controlled impedance PCBs is well documented. As more designs require fast data rates, and shrinking dies on new silicon mean edge-speeds on existing designs may be faster than originally anticipated, the need to take care over signal integrity becomes an important part of the design process. However, good design doesn't conclude when you output your designs to the fabricator. Unless you work in close partnership with your PCB supplier, the care that you have taken over signal integrity at the design stage may be compromised in production.

#### **INTRODUCTION**

A key factor in producing good yields of high-quality PCBs containing controlled impedance traces is the relationship between the circuit designer, the PCB layout engineer, and the front-end and process engineers at the PCB fabricator. Accurate traceable and repeatable test results are the key to feeding production data back into the production process in order to increase yields and therefore lower unit costs.

#### REPEATABILITY AND REPRODUCIBILITY

Reproducible measurements are important because boards are often designed in one location, prototypes built at another, then volume production moves to a third location, often in Asia. Or maybe production is simply moved from a local fast-turn shop to a volume shop as production ramps up.

- There are two main considerations:

- 1. Absolute accuracy of measurement

As with all measurements, the measurement equipment should be calibrated to an

international standard. While impedance is measured in Ohms it would seem logical to use a range of precision resistors to calibrate the impedance test equipment. However, the test instrument of choice for controlled impedance test is in most cases a Time Domain Reflectometer. TDRs can be calibrated with a resistive load—but it's not so well known that if you calibrate a TDR with a resistive load you should make the measurements with the same terminated conditions. This is not very practical as most tests will be performed on coupons or test traces built into the board. At test time these will be unterminated, i.e. they will end in an open circuit. (This is because the change in DC conditions in the pulser sampler caused by the presence of the termination resistor can cause an offset in the output level of the pulse-in the worst case this can contribute up to 3 or  $4\Omega$  measurement error on a 50 $\Omega$  line). Because measurements are made on unterminated lines, you should calibrate the TDR with an unterminated reference. A precision reference airline is the recommended standard for impedance measurement.

Figure 1. Traceable Reference.

To verify the accuracy of a differential TDR system, a matched pair of traceable single ended air-lines should be attached to the two differential outputs. This provides an acceptable verification for differential TDRs, as true differential reference impedance standards are not available. If a pair of 50 $\Omega$  lines are used the TDR will see 100 $\Omega$  differential, a pair of 75 $\Omega$  lines will let the TDR see 150 $\Omega$  differential impedance.

Should there be a disagreement over a measurement between OEM and PCB fabricator, the use of traceable air-lines to verify the measurement equipment should help overcome any issues surrounding the type of measurement equipment used at each site. A note on air-line calibration:

The impedance of an air-line is determined by the ratio of the bore of the outer conductor to the diameter of the inner conductor. National standards labs use a technique called air gauging to accurately measure the bore of the outer conductor. The air line impedance is calculated as:

Zo = 59.939 log<sub>e</sub> (D/d) where D is the diameter of the inner conductor and d is the bore of the outer conductor. If you would like to learn more about traceable air-line calibration you may like to read: *Traceability for Radio Frequency Coaxial Line Standards.*<sup>1</sup>

2. Measurement repeatability

A number of factors can influence measurement repeatability:

- Test fixtures

- Operator

- · Test probes

- Test cables

- Test equipment

- External influences

Test fixtures are important when testing boards using surface structures; it is important that a surface microstrip or co-planar line is of sufficient distance from another surface to avoid the adjacent surface acting as an extra dielectric layer. For example, a coupon or board with microstrips on the top and bottom layer needs to be either turned over when testing the bottom layer or supported above the table surface.

Operator training is vital with manual test systems. Poor probing or placing fingers or resting hands on a test trace can influence impedance measurement.

Test probes have a finite life, connection aberrations will worsen with use and spring test pins develop series resistance. This tends to be more of an issue where boards are being tested for impedance 24 hours a day, 7 days a week.

Dispose of worn probes! One major PCB vendor suffered an embarrassing and expensive claim where an operator had decided to fit worn probes to a TDR "because they read high" to allow a batch of low reading boards to pass . . . The cause of the out-of-spec shipment was discovered whilst the fabricator's customer was on a tour of the facility.

Test cables also have a finite life. Good RF cables have a solid silver-coated core—this core will age and gradually degrade the measurement. Ultimately, they will go open circuit. In high throughput environments they should be regularly replaced.

TDRs are used by most designers and PCB fabricators. TDR sampling-heads drift with time and temperature, so for critical applications regular recalibration to a standard is required. Some systems are equipped with an internal stable reference impedance which is used for recalibration at automatic intervals. This is ideal in a production environment. Care should be taken with all TDRs to prevent ESD damage. High-speed TDR pulser samplers are susceptible to electro static discharge damage and good ESD practice is important.

Finally, repeatability can be influenced by external RF sources, especially when you are testing traces on outer layers. One of the main sources of external RF can be a mobile phone near the test system. It is recommended that all phones are switched off in the area of an impedance test system, as test coupons with surface traces act as an excellent antenna. This effect was noticed at Polar during long term R+R testing of automated systems when a mobile was inadvertently left in the test area.

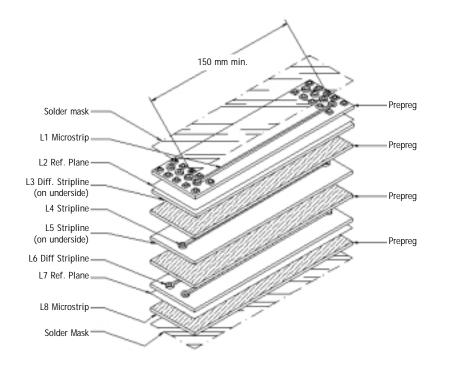

Figure 2. Exploded Diagram of Test Coupon.

## Test probes have a finite life, connection aberrations will worsen with use and spring test pins develop series resistance. This tends to be more of an issue where boards are being tested for impedance 24 hours a day, 7 days a week.

#### TESTING WITH COUPONS FOR PROCESS QUALIFICATION AND PRODUCTION TEST

It is common practice for board manufacturers to check controlled impedance build-integrity initially by building engineering lots of prototype boards and even panels of coupons to verify copper weight, line widths, dielectric thickness and constant across each panel and each batch before beginning volume production.

Even in production it's common to perform 100% controlled impedance testing on controlled impedance boards (in fact, 100% controlled impedance testing will probably be part of the acceptance criteria for the board). Why use test coupons?

When testing a controlled impedance PCB, however, you'll frequently run into practical difficulties. For example, it's not uncommon for a controlled impedance trace to be inaccessible for verification. Although it may be possible to add extra pads and vias to test the trace on the PCB, doing so will effect the circuit performance and will occupy valuable board space.

You may encounter other challenges in testing:

• Planes are not interconnected on the PCB and this can result in inaccurate measurements.

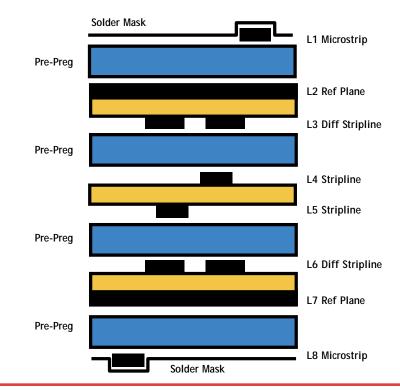

Figure 3. Profile of Coupon Layers.

If you are designing coupons for automated systems it is best to use a small test pad as a probing point. However, if you are designing coupons for manual test, a via hole makes it easier to register a probe. Small pad size is ideal for RF performance, but if you make the pads too small they will be very difficult to probe manually.

- To achieve accurate and consistent test results, testing should be performed on straight single traces of ideally 150mm in length—the actual PCB traces will often be much shorter.

- PCB traces are rarely simple straight lengths of copper—they'll normally include branches to circuit components and vias between layers, making accurate measurements very difficult.

- To obviate some of these difficulties,

testing is normally performed, not on the board itself, but on a test coupon manufactured at the same time and on the same panel as the PCB.

#### **TEST COUPONS**

Test coupons are typically small PCBs, approximately 160 x 30 mm, with exactly the same layer and trace construction as the main PCB—with one exception. On a coupon the Vcc and ground planes are all intentionally shorted together to simulate the RF conditions on a finished assembled board.

For example, a coupon will include traces of the same line width and copper weight on the same layer as the controlled impedances on the main PCB. The coupon will be located so as to represent actual board conditions for plating, etching, and lamination. It's common practice to fabricate one coupon at each end of a board panel to verify consistency of performance across the whole panel

At the time the artwork is produced, the same aperture code used for the controlled impedance traces is used to produce the test traces on the coupon. The coupon is fabricated at the same time as the main PCB so the coupon will exhibit the same impedance as the PCB. The impedance of a trace is dependent upon all the PCB's dimensions and electrical properties, so the use of coupons for testing is an accurate, reliable, and proven method for manufacturing quality and consistency.

#### PROFILE OF CONTROLLED IMPEDANCE LAYERS IN TEST COUPON

The coupon will use the same solder mask requirements as the board. The pattern of conductors on the coupon will be designed to reproduce conditions on the board.

#### DESIGN FOR IMPEDANCE TEST

Whether you are testing on coupons, or if space allows and you have built special test traces in your boards, please consider design for impedance test.

Orientation. Testing is simplified if all test signal/ground pairs are oriented the same way. RF test cables are not very flexible and an operator will take longer if the probe needs rotating 90 degrees for each test. This is also true for automated systems. Also try to standardize coupon footprint, as this will reduce the number of probe variations you require.

If you are designing coupons for automated systems it is best to use a small test pad as a probing point. However, if you are designing coupons for manual test, a via hole makes it easier to register a probe. Small pad size is ideal for RF performance, but if you make the pads too small they will be very difficult to probe manually. Sample coupon Gerber is available from Polar and also in IPC-D-317.

#### TEST SYSTEMS

Most impedance test systems will be used by

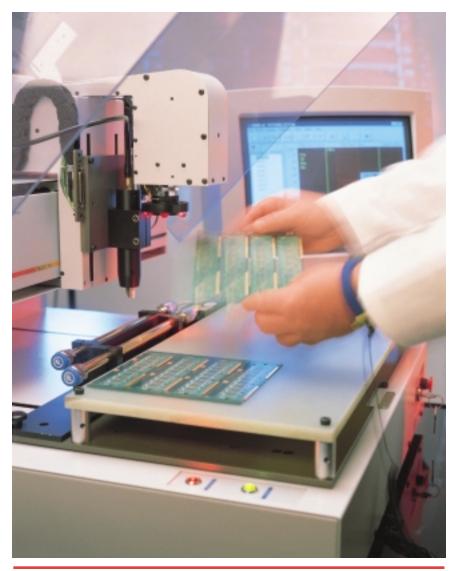

Figure 4. Automated Impedance Test.

non-technical operators, often for many hours a day. Also, in many mid-sized shops, the systems are set up by process or production engineers who may not have an electronics background. Set-up on Polar CITS500s is simply a case of entering a list of impedance values tolerances and setting for single ended or differential test. Operators advance through coupon tests by use of a foot pedal with minimum need for mouse or keyboard input.

Where high volume test is required there is a choice between a fixture and flying probe-based system. At first look, it would seem that a fixture based system would offer the best throughput. However, unlike in BBT open and shorts test, a TDR test takes just under one second for single-ended measurement and around 1.5 seconds for differential. Therefore, move time on a flying probe system is not a great factor in test speed. More important is that a flying probe impedance test system such as Polar RITS500s can self-verify at the probe tip. This is achieved through the use of built-in traceable air-lines on the test table itself. Fixture based test systems using a matrix of RF coaxial switches cannot self-verify in this way and, as a result, flying probe impedance test systems can be designed with inherently better gage R+R.

Figure 5. Onboard Verification.

## The best PCB fabricators take statistical data from impedance test and feed it back into the production process.

To protect against static damage, automated systems should perform a board discharge, then test, then discharge again for maximum protection of the TDR heads.

#### ACHIEVING HIGH YIELDS

The best PCB fabricators take statistical data from impedance test and feed it back into the production process. Often this data suggests that nominal line widths may need to be altered from the original design. This comes as something of a surprise to many PCB designers who are accustomed to submitting Gerber to the PCB manufacturer who then turns the data into finished boards without adjustment.

High-end CAD systems calculate line widths using advanced mathematical tools called field solvers; however, these tools give you an ideal-world calculation of line width. Real PCBs will differ depending on the source of prepreg and core materials, the glass resin ratio after pressing, and the etched trace geometry. Ideally, you should identify controlled impedance traces with a separate aperture code from other traces of the same nominal width. If possible, allow the front-end engineers to alter the nominal

# **INTERVIEW: MARTYN GAUDION**

line width (within design constraints) to achieve maximum yields for impedance.

Here are some real examples of what happens when communication is poor or non-existent between designer and fabricator—some have cost money, others are simply inconvenient:

PCB Fabricator has to obtain waiver to ship out-of-spec line width on boards in order to meet impedance requirements. Not just once, but for every repeat order of one particular job.

PCB Designer specifies "free build" on a multilayer that should be impedance controlled. The fabricator makes a stack up without consideration of impedance and the boards all fail incoming QA.

Specifications are "cut and pasted" from one design to another, the PCB fabricator is then fed confusing information such as specs for impedance controlled lines on maximum copper layers.

#### CONCLUSIONS

Board costs can be minimized by developing a good working relationship between the PCB design team and the PCB fabricator. In boards where signal integrity is important, the PCB fabricator has a crucial role to play in ensuring designs are accurately realized. This means that the fabricator may need to alter design data—this is especially the case on fine line boards. Making this transition requires trust and confidence in your PCB vendor. Accurate and repeatable impedance test systems are key to building this relationship. ■

#### REFERENCES

- 1. Ide, J. P. "Traceability for Radio Frequency Coaxial Line Standards." National Physical Laboratory, 1992.

- 2. Polar Instruments. "An Introduction to the Manufacture of Controlled Impedance PCBs."

- 3. J. Alan Staniforth, Gary Rich, Chris Gregg. "Calculation of the Differential Impedance of Tracks on FR4 Substrates." Proceedings, IPC Expo, San Diego, CA. April 2000, p.S11-1-1.

- 4. Controlled Impedance design and test: www.developer.intel.com/design/chipsets /appl...pcd\_pres399.htm.

**TBA:** How is Controlled Impedance Test perceived in the HDI industry? What is the percentage of HDI manufacturer using such process? For what kind of applications?

**Gaudion:** Many HDI boards have controlled impedance requirements. The requirement for impedance control is the same on HDI as on conventional PCBs. When edge speeds are fast and traces are long in comparison, then impedance needs to be taken into account. One additional point worth noting is that on boards where the design is for both low voltage and high speed, the noise margins will be lower and hence more susceptible to changes in impedance causing reflections.

**TBA:** What are the main characteristics (technical and economical) Controlled Impedance Test equipment has to address, depending on applications (mainstream PCBs, HDI PCBs, etc.) now and in the near future?

**Gaudion:** Like all test methods, the sooner you can check characteristics, the better. If a board can be tested before resist and nomenclature is added then problems can be resolved before too much value is added to the product. You must, however, take into account the effect of adding resist after the test. Some fabricators test at both stages. This is especially important for prototype shops where fast turn around is essential.

As manufacturers push for higher speeds there is a trend to ask for  $\pm 5\%$  tolerance rather than 8–10% on older designs. Although these tolerances seem loose in absolute terms, from a RF perspective, 5% is quite a tight tolerance to achieve. It is essential that in order to avoid rejecting good boards, your test system has excellent R+R, and this should also limit or minimize disputes on specification with your customers.

TBA: Above which frequency (or other factors) should controlled impedance test be required on a test coupon

**Gaudion:** Test coupons are the best solution for impedance test. They ensure repeatable measurements. In general, the higher the frequency and faster the edge-speed, the more critical the need to test. Also when working on fine lines or outer layers where the etching is approaching its limits, yields will reduce. So, while a fabricator may be able to make good yields on 200 micron line widths, the yields may not be economic at 100 microns. It is essential for designers and PCB fabricators to co-operate to achieve high yielding designs.

TBA: As a 100% basis (every board tested)?

**Gaudion:** Expensive boards! If you make high value boards, especially in lower volumes where you do not have enough data to statistically fine tune the process, then it is essential to test a coupon per board. On very critical applications, the coupons may be designed into the board itself.

TBA: How will the proportion of PCBs tested for controlled impedance increase in the future?

**Gaudion:** Some high-end shops are already building over 90% impedance controlled boards. In this case, sometimes all boards have a coupon added to the panel and are treated as impedance controlled. The non-impedance-controlled boards become the exception in this case. The requirement depends on application but the increase in high speed and wireless communications means that many shops working on high-end production will produce over 80% controlled impedance boards. In conclusion, the most important factor when moving to controlled impedance is to establish a good relationship between PCB designer and controlled impedance PCB fabricator.