What's new in

Speedstack 2009?

Application Note AP518

"Thank you for the email to upgrade Speedstack and Si9000e. I have been using this toolset along with Allegro® for all my board designs. It has increased my confidence to 100% for me and my customers as I have been doing 12 and 14 layer designs. The numbers are dead on for the manufacturing group and the flow is so easy between me and my customers. Thank you again for such a wonderful toolset. Have a great day!"

William

Hardin

PCBSService, Inc.

http://www.pcb4service.com

Polar's Speedstack 2009 PCB Stackup Builder introduces powerful enhancements to the AutoStack VSR (Virtual Stack Realisation) engine along with new interfaces to industry standard systems.

- Laser

drill rules ensures

compatibility with drill capability

- Partial stack definition allows you to take control of critical dimensions, and let Autostack fill in the rest

-

Enhanced Virtual Stack Realisation engine enhances the build of low layer count stacks

-

Mania Barco Ucam .Job file format import

Laser drill rules

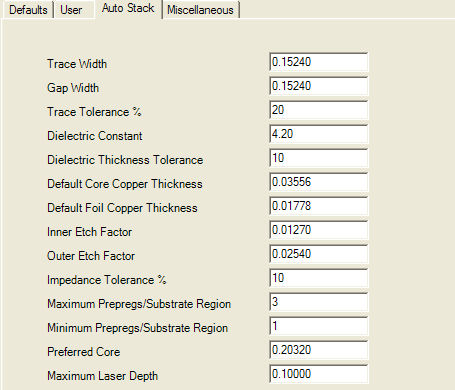

Speedstack 2009's Configuration Options include, in the Auto Stack settings, the facility to add a laser drilling maximum depth rule setting. The user can specify the maximum drillable height for laser drills in order to limit the dielectric height for certain regions within the stackup.

Auto Stack Configuration Options

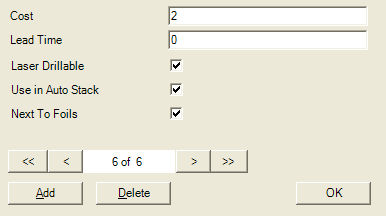

Users can add a flag to a material library to specify laser drillable materials. Double clicking a prepreg material type in the library displays the Properties dialog. Prepreg materials include the Laser Drillable option to specify a material as laser drillable click the associated check box (below).

Material properties dialog

Partial stack definition

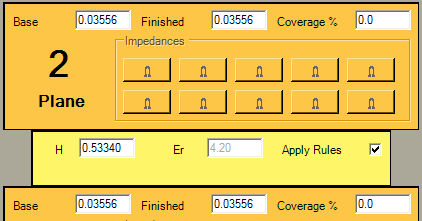

Speedstack 2009 allows partial stack definition i.e. the user can specify critical minimum or maximum dielectric heights within the stackup and allow Speedstack's Autogenerate to allocate the values for other layers. Within the Stack Definition window, select the prepreg or core layer and specify the parameters for the selected layer.

Selected layer with height rules specified

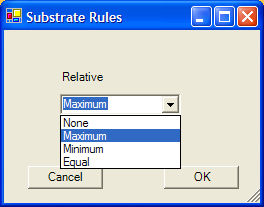

Clicking the Apply Rules check box displays the Substrate Rules dialog and allows the user to specify maximum or minimum height values for the selected core or prepreg or to specify the actual height value.

Substrate Rules dialog

When Autogenerate creates the stackup the height rules specified for the selected layers are applied. Adjustments will be made as defined by the chosen substrate rules for the selected layers Autogenerate will allocate height values for other layers to meet the overall board height specifications.

Enhanced virtual stack realisation engine

When target board thickness can not be achieved due to impedance structure requirements, Speedstack 2009 provides adjustment algorithms (similar to the Si8000m/Si9000e sensitivity analysis function) to adjust the structure height to achieve the target board thickness.

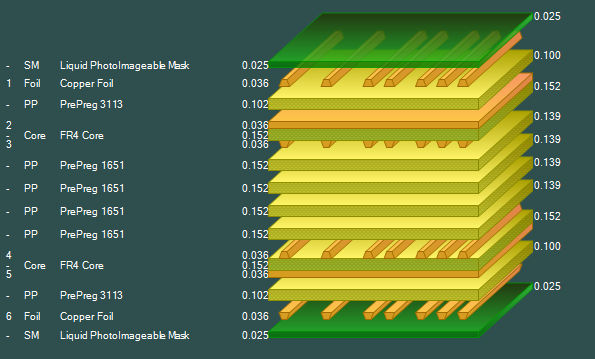

In this example stackup the screen shot below represents the stack produced by Speedstack without stack padding adjustments to achieve target impedances of 60 Ohms on each of the controlled impedance structures. Speedstack produced a board 38 mil thick with the impedances exactly on target.

Stackup with board thickness 38 mil (0.96 mm)

In this case, however, the customer requires a board thickness of 50 mil (1.27mm). Speedstack 2009 incorporates height adjustment algorithms that will pad the board with suitable materials while maintaining the target impedances within tolerance.

The padded stackup - board thickness 50 mil (1.27 mm)

The graphic above illustrates the padded stack (with extra prepreg material). The final board height of 50 mil (1.27mm) has been achieved and the final impedance values (62.6 Ohms in this example) remain within specification without trace modification.

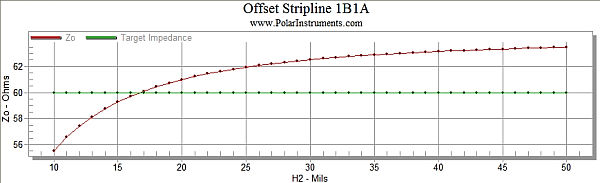

The effects of varying height on the impedance can be graphed using the Sensitivity Analysis tab on the Si8000 or Si9000 Field Solvers below.

Si8000 Sensitivity Analysis graph Z0 v H2 for the offset stripline structure

Mania Barco Ucam .Job file format import

Speedstack 2009 enhances its integration with other systems and is able to import Mania Barco .Job files as used by Ucam and Integrator.

Speedstack is now in worldwide use with a major OEMs, PCB brokers and procurement

engineering teams, these Speedstack customers report both

significant time saving in stack creation and improved communication between design and fabrication.

Allegro® is registered trade mark of Cadence Design Systems, Inc.