## Polar Fehlerdiagnosesystem

# PFL Bedienerhandbuch

**Polar Instruments Ltd**

Polar Instruments Ltd. Garenne Park St. Sampson Guernsey Channel Islands GY2 4AF ENGLAND

Fax: +44 (0)1481 52476

MAN 160-9703

### PFL760/780 FEHLERDIAGNOSESYSTEM HANDBUCH

### **GARANTIE**

POLAR Instruments Ltd. sowie der autorisierte Vertreter gewähren für dieses Gerät eine Garantie für die Dauer eines Jahres. POLAR Instruments Ltd. sowie der autorisierte Vertreter behalten sich vor, das Gerät zu reparieren oder zu ersetzen, falls Material- oder Verarbeitungsmängel die Ursache eines Defekt sind. Diese Garantie gilt ausschließlich unter der Bedingung, daß das Gerät ordnungsgemäß verwendet und entsprechend den Instruktionen von POLAR serviciert wurde.

Veränderungen am Gerät, Mißbrauch, Beschädigung, Reparaturen oder Reparaturversuche durch nicht autorisierte Personen führen zum Verlust des Garantieanspruches. POLAR Instruments Ltd. sowie der autorisierte Vertreter übernehmen keine Haftung für Schäden, die durch die Verwendung dieses Gerätes entstehen könnten.

Copyright Reischer Industrie-Elektronik, 1997

Microsoft und MS-DOS sind eingetragene Namen der Microsoft Corporation.

IBM ist das eingetragene Warenzeichen der International Business Machines Corporation.

## Inhalt

| Konformitätserklärung                          | 1  |

|------------------------------------------------|----|

| ELEKTROMAGNETISCHE VERTRÄGLICHKEIT             | 1  |

| SICHERHEIT                                     | 2  |

| ACHTUNG                                        | 2  |

| SCHUTZERDE                                     |    |

| Netzkabel Farbcodierung:                       |    |

| NETZVERSORGUNG                                 | 2  |

| Netzspannungseinstellung                       |    |

| PFL BETRIEB                                    |    |

| VORSICHTSMASSNAHMEN                            |    |

| Elektrische Isolation                          | 3  |

| Spezifikationen                                | 4  |

| ASA Test Funktionen                            | 4  |

| ICT Funktionen (nur PFL780)                    | 4  |

| Betriebsbedingungen                            |    |

| Netzversorgung                                 |    |

| Kanal A und B Schutzsicherungen                |    |

| Abmessungen (ohne Zubehör)                     |    |

| Symbole                                        |    |

| ZUBEHÖR                                        |    |

| Standardzubehör                                |    |

| Optionales Zubehör                             | C  |

| Einführung POLAR PFL Fehlerdiagnosesystem      | 7  |

| Das PFL Fehlerdiagnosesystem                   | 7  |

| Analoge Signaturanalyse                        | 7  |

| Der Pulsgenerator                              | 7  |

| In Circuit Test                                |    |

| Anzeige von Verbindungen und logischen Fehlern | 8  |

| Die PFL Bauteilbibliothek                      |    |

| Anwendungsgebiete                              |    |

| PC-Steuerung                                   |    |

| Systemanforderungen                            | 9  |

| Installation des Systems                       | 11 |

| Auspacken                                      | 11 |

| Anschluß des PFL an die Netzversorgung         | 11 |

| Installation der PFL Software                  |    |

| Auswahl der PFL Gerätetype                     | 13 |

| Anschluß des Computers an den PFL              | 13 |

| Start des Programms                            |    |

| Der Hauptschirm                                |    |

| Systemkonfiguration                            |    |

| Einstellung der PFL Steuersoftware             |    |

| Systemsicherheit                               | 15 |

|        | Ausstieg aus der PFL-Software                      | 17 |

|--------|----------------------------------------------------|----|

| Allger | neine Beschreibung                                 | 18 |

|        | Analoge Signaturanalyse                            | 18 |

|        | In-Circuit Test                                    |    |

|        | Bedienungselemente und Anschlüsse                  |    |

|        | Die PFL Frontplatte                                |    |

|        | Die PFL Rückwand                                   | 20 |

| Erste  | Schritte mit dem PFL                               | 21 |

|        | Das Live-Instrument                                | 21 |

|        | Das Live-Instrument                                | 21 |

|        | Verwendung der PFL Prüfspitzen                     | 21 |

|        | Einstellung der Prüfbedingungen                    | 22 |

|        | Testspannungswahl                                  | 22 |

|        | Pulsgeneratorausgänge                              | 25 |

|        | Test integrierter Schaltungen                      |    |

|        | Bauteiltest mit Quicktest                          |    |

|        | Vergleichstests mit Quicktest                      |    |

|        | Einzelboardtest mit Quicktest (nur PFL780)         | 35 |

| Asa B  | auteiltest                                         | 37 |

|        | Signaturformen                                     | 37 |

|        | Test passiver Bauteile mit ASA                     |    |

|        | Test von Widerständen                              |    |

|        | Test von Kondensatoren                             | 40 |

|        | Test von Induktivitäten                            | 42 |

| ASA 1  | Test von Halbleitern                               | 43 |

|        | Test von Dioden, LEDs und Zenerdioden              | 43 |

|        | Test von Transistoren                              |    |

|        | Test von Junction Field Effect Transistors (JFETs) | 48 |

|        | Test von MOSFETs                                   | 49 |

|        | Test von Spezialbauteilen                          | 50 |

|        | Test von Optokopplern                              |    |

|        | Test von Vierpolen                                 | 51 |

| Test i | ntegrierter Schaltkreise mit ASA                   | 54 |

|        | Integrierte Schaltkreise                           | 54 |

|        | Bauteiltests in der Schaltung                      | 58 |

|        | Busbausteine                                       |    |

| ICT B  | auteiltest                                         | 60 |

|        | PFL780 In Circuit Funktionstest                    | 60 |

|        | Bauteiltest mit ICT                                |    |

|        | Test von Bausteinen in der Schaltung               |    |

|        | Backdriving                                        |    |

|        | Die PFL780 Bauteilbibliothek                       |    |

|        | Ict Test von Digital-IC's                          |    |

|        | Der ICT unter Versorgungsspannung                  |    |

|        | Der Verbindungstest                                | 64 |

|        | Der Funktionstest                                  |    |

|      | Kontrolle der Testbedingungen                   |    |

|------|-------------------------------------------------|----|

|      | Speichern und Testen digitaler IC's             |    |

|      | Test des Bausteins                              | 67 |

|      | Das Verbindungsdiagramm                         | 67 |

|      | Stuck pins                                      |    |

|      | Anwendungshinweise                              | 68 |

|      | Loop until Pass bei instabilen ICT-Ergebnissen  |    |

|      | Initialisierung von Bauteilen                   |    |

|      | Isolieren von Bauteilen in der Schaltung        |    |

|      | Busverbundene (tristate) Bausteine              |    |

|      | Dusverbundene (tristate) Dausteine              |    |

| Sch  | reiben von Testprogrammen                       | 73 |

|      | Das Programmfenster                             | 73 |

|      | Sichern von Testprogrammen                      |    |

|      | Arbeiten mit Testprogrammen                     | 7/ |

|      | Erzougen eines neuen Testprogramme              |    |

|      | Erzeugen eines neuen Testprogramms              |    |

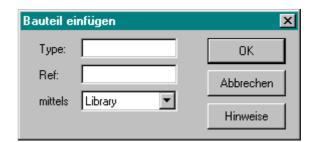

|      | Hinzufügen von Bauteilen in die Testliste       |    |

|      | Baugruppenhinweise                              |    |

|      | Speichern des Testprogramms                     |    |

|      | Benennen von Testprogrammen                     |    |

|      | Ansicht von ASA Signaturen                      |    |

|      | Ansicht von ICT Daten                           | 79 |

|      | Das Logikdiagramm                               | 79 |

|      | Ansicht von Links Daten                         | 80 |

|      | Boardtest                                       |    |

|      | Test eines Boards                               |    |

|      | Fortgeschrittenes Editieren                     |    |

|      | Einsatz des Parametereditors                    |    |

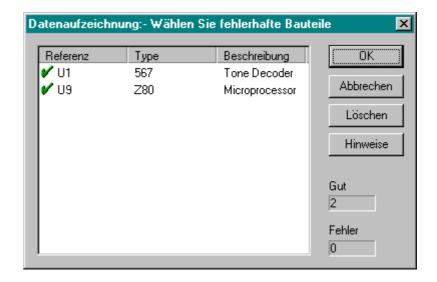

|      | Datenaufzeichnung                               |    |

|      | Die PFL Datenaufzeichnung                       |    |

| Hinz | zufügen von Bauteilen zur Bibliothek mit DevLib | 89 |

|      |                                                 |    |

|      | Die PFL Benutzerbibliothek                      |    |

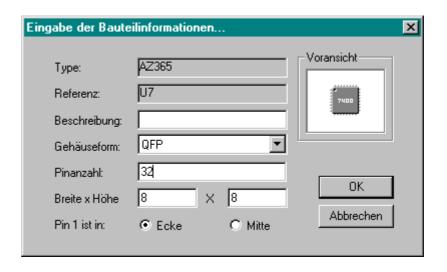

|      | Hinzufügen eines neuen Bausteins zur Bibliothek |    |

|      | Erzeugen von Alias-Bezeichnungen                | 90 |

| War  | rtung und Reinigung                             | 93 |

| vvai | itung unu Nemigung                              | 9. |

|      | Servicieren des PFL                             | 93 |

|      | Erforderliche Kalibration                       | 93 |

|      | Fehlersuche                                     | 93 |

|      | Reinigung                                       |    |

|      | Technische Unterstützung                        |    |

|      | •                                               |    |

| Anh  | nang A - Beispiele von Analogsignaturen         |    |

| Anh  | nang B – Der Signaturvergleichsalgorithmus      |    |

| Anh  | nang C – PFL Pin-Numerierungsformate            |    |

| Anh  | nang D – SMD Prüfspitzen                        |    |

|      |                                                 |    |

Pinnumerierung

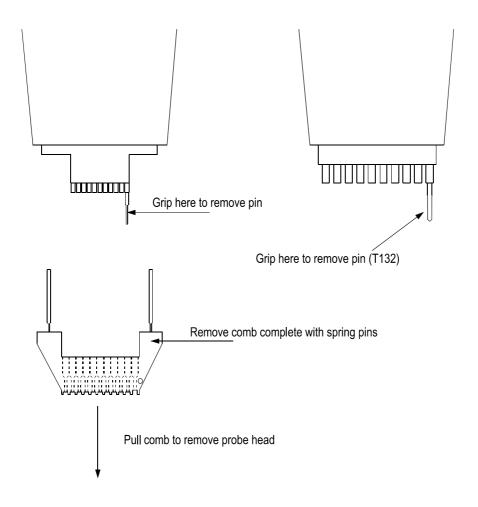

### Verwendung der Prüfspitze Austausch der Nadeln

Kontaktierung von DIL ICs

Kontaktierung von SOIC's

Kontaktierung von PLCC's, QFP's, etc.

## Konformitätserklärung

### **ELEKTROMAGNETISCHE VERTRÄGLICHKEIT**

### Erklärung der Einhaltung von EU-Richtlinien

Dieses Produkt stimmt überein mit den Schutzmaßnahmen der EC Council Directive 89/336/EEC für die Angleichung der Richtlinien der Mitgliedsstaaten in Bezug auf elektromagnetische Verträglichkeit.

Eine Konformitätserklärung entsprechend den Anforderungen der Richtlinie wurde unterzeichnet durch:

POLAR INSTRUMENTS (UK) LTD 11 College Place London Road Southampton England SO1 2FE

Dieses Produkt entspricht EN50081-1:92 und EN 50082-1:92

### **SICHERHEIT**

#### **ACHTUNG**

Sowohl Phase als auch Neutralleiter dieses Gerätes sind gesichert.

Das Gerät enthält keine vom Anwender servicierbaren Teile. Wenn das Gerät an die Netzversorgung angeschlossen ist, so können nach dem Öffnen des Gehäuses gefährliche Spannungen zugänglich sein. Um die Sicherheit des Anwenders zu gewährleisten, betreiben Sie dieses Gerät nur mit vollkommen geschlossenen Gehäuse.

#### **SCHUTZERDE**

Dieses Gerät muß korrekt mit Schutzerde verbunden werden. Betreiben Sie das Gerät ohne angeschlossener Schutzerde. Stellen Sie sicher, daß Gerät nur an eine Steckdose mit Schutzleiter angeschlossen wird. Achten Sie bei Verwendung eines Verlängerungskabels auf korrekte Schutzleiterverbindung..

Hinweis: Dieses Gerät ist mit einem dreipoligen Schutzkontaktstecker versehen. Falls ein spezieller Stecker zu Anpassung an die lokale Netzversorgung erforderlich ist, so lassen Sie diesen nur von einem Fachmann montieren. Der abgezwickte Stecker muß ordnungsgemäß entsorgt werden.

#### Netzkabel Farbcodierung:

Braun Phase

Blau Nulleiter

Grün/Gelb Schutzleiter

#### **NETZVERSORGUNG**

#### Netzspannungseinstellung

Prüfen Sie ob die Netzspannungseinstellung wie auf der Geräterückseite angegeben mit der lokalen Netzspannung übereinstimmt.

Lassen Sie Änderung der Netzspannungseinstellung nur durch einen Fachmann durchführen. Die Anleitung zur Netzspannungseinstellung finden Sie im von POLAR Instruments herausgegeben PFL Servicehandbuch.

#### **PFL BETRIEB**

Dieses Dokument beinhaltet Instruktionen und Hinweise, welche vom Anwender unbedingt eingehalten werden müssen, um den sicheren Betrieb zu gewährleisten. Jede Verwendung des Gerätes in einer anderen als im Handbuch beschriebenen Weise kann dazu führen, daß die Sicherheitsvorkehrungen im Gerät außer Kraft gesetzt werden und ein sicherer Betrieb nicht mehr gegeben ist. Bewahren Sie diese Instruktionen sorgsam auf.

Das Gerät ist nur für den Betrieb in Räumen entwickelt und sollte in einer Werkstättenumgebung auf einem stabilen Tisch aufgebaut werden.

Verwenden Sie nur Originalzubehör (z.B. Prüfspitzen und Testclips) von POLAR Instruments.

Das Gerät darf nur von einem Fachmann entsprechend den Herstelleranweisungen gewartet und repariert werden.

Erfolgte eine Beschädigung der Sicherheitsvorkehrungen, so ist das Gerät außer Betrieb zu nehmen, gegen Inbetriebnahme zu sichern und an qualifiziertes Servicepersonal weiterzugeben.

Eine Beschädigung der Sicherheitsvorkehrungen könnte erfolgt sein bei:

Sichtbaren Zeichen von mechanischer Beschädigung normaler Betrieb It. Anweisungen im Handbuch nicht möglich

Längerer Lagerung unter ungünstigen Bedingungen Übermäßiger Beanspruchung während des Transports

Eindringen von Flüssigkeiten

#### VORSICHTSMASSNAHMEN

### **Elektrische Isolation**

Isolieren Sie das Meßobjekt immer von der lokalen Stromversorgung (inkl. Schutzleiter) bevor Sie den PFL anwenden.

## Spezifikationen

### **ASA Test Funktionen**

| Testkanäle                              | 128                                                    |

|-----------------------------------------|--------------------------------------------------------|

| Testbereiche                            | Vpk lpk                                                |

| Junction<br>Logic<br>Low<br>Med<br>High | 1V 500µA<br>10V 5mA<br>10V 150mA<br>20V 1mA<br>40V 1mA |

| Testfrequenzen                          |                                                        |

| Low<br>Medium<br>High                   | 90Hz<br>500Hz<br>2kHz                                  |

| Pulsgenerator                           |                                                        |

| DC, Pulse1, Pulse2                      | 0 – ±5V variabler Pegel<br>Pulsbreite variabel         |

| Toleranzeinstellung                     | 1 – 99%                                                |

| Aufzeichnung der Testergebnisse         | ✓                                                      |

## ICT Funktionen (nur PFL780)

| Testkanäle                 | 40                                                                       |

|----------------------------|--------------------------------------------------------------------------|

| Spannungs-Schwellwerte     | TTL, CMOS,<br>Benutzerdefinierbar                                        |

| Guard-Ausgänge             | 4 x High, 4 x Low                                                        |

| Testzeit                   | <16ms (bei 100% Step Rate)<br>entspricht INT DEF STAN 00-53/1            |

| Verbindungstest            | Identifiziert verbundene Pins                                            |

| Eingebaute Stromversorgung | 5V, 5A<br>(nur während ICT-Test aktiv)<br>gesichert durch 5A T Sicherung |

### Betriebsbedingungen

Das Gerät ist nur für den Betrieb in Räumen unter folgenden Betriebsbedingungen entwickelt.

| Höhe                      | Bis zu 2000m                                                            |

|---------------------------|-------------------------------------------------------------------------|

| Temperatur                | +5°C to +40°C Umgebungstemp.                                            |

| Relative Luftfeuchtigkeit | RH 80% maximum bei 31°C — fällt linear auf 50% bei 40°C                 |

| Netzgebundene Störungen   | Lt. Installationskategorie II<br>(Übrspannungskatgorie II) in<br>IEC664 |

| Verschmutzungsgrad        | 2 (IEC664)                                                              |

### Netzversorgung

$230V \pm 10\%$ ,  $115V \pm 10\%$  oder  $100V \pm 10\%$  mit 50/60Hz, 110VA.

### Kanal A und B Schutzsicherungen

160mA Flink

### Abmessungen (ohne Zubehör)

Abmessungen Breite 443 mm

Höhe 114 mm

Tiefe 280 mm

Gewicht 7.0kg

### **Symbole**

Die folgenden Symbole werden im Gerät verwendet.

ACHTUNG Um Schäden am Gerät zu vermeiden und den sicheren Betrieb zu gewährleisten, beachten Sie die Anweisungen im Handbuch, wenn Sie Verbindungen zu Anschlüssen mit diesem Symbol herstellen.

— COM Dieser Anschluß ist intern mit dem Schutzleiter verbunden (Erde).

## **ZUBEHÖR**

### Standardzubehör

| PFL Software                           | FSW144              |

|----------------------------------------|---------------------|

| Prüfspitzenset                         | MMP159              |

| Rote und schwarze Prüfleitung          | ACC110, ACC111      |

| Pulsgeneratorleitung, blau, 2 Stk.     | ACC112              |

| Stromversorgungsleitung                | ACC151 (nur PFL780) |

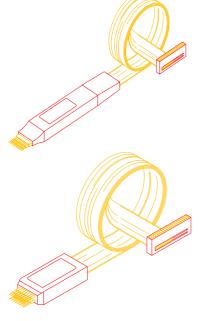

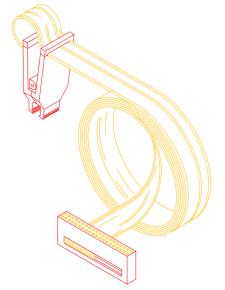

| 16 poliger Testclip mit Flachbandkabel | ACC107              |

| 40 poliger Testclip mit Flachbandkabel | ACC106              |

| Fußpedal                               | ACC124              |

| RS-232 Interfacekabel                  | ACC142              |

| Zubehörtasche                          | ACC105              |

| Bedienerhandbuch                       | MAN160              |

| Netzkabel                              |                     |

## Optionales Zubehör

| Adapter Board                          | T41282      |

|----------------------------------------|-------------|

| Adapter für PC AT-Direktsteckverbinder | T41283      |

| Nullkraftsockeladapter                 | ACC145      |

| Gerätetragetasche                      | ACC125      |

| SMD-Prüfspitzen                        | T131 – T141 |

| 9 – 25 Pin RS232 Adapter               | ACC127      |

| SOIC Test Clip Set                     | ACC160      |

| PLCC Test Clip Set                     | ACC161      |

| DIP IC Test Clip Set – 6 Typen         | ACC140      |

| DIP IC Test Clip Set – 10 Typen        | ACC139      |

| ICT-Treiber-Entwicklungssoftware       | ACC179      |

## Einführung POLAR PFL Fehlerdiagnosesystem

### Das PFL Fehlerdiagnosesystem

Der PFL ist ein schnelles und effizientes Mittel zum Test von elektronischen Komponenten sowohl isoliert als auch im eingebauten Zustand. Der PFL wird von einem IBM- oder Kompatiblen PC unter Windows 95 Betriebsssystem gesteuert.

Der PFL760 und PFL780 bietet die Funktionen und Umgebung zur Erzeugung von Testprogrammen für die Überprüfung einer Vielzahl von elektronischen Komponenten; der PFL760 basiert auf dem effizienten Verfahren der Analog-Signaturanalyse, der PFL780 kombiniert Analog-Signaturanalyse mit dem zusätzlichen Digital-In-Circuit-Test.

### **Analoge Signaturanalyse**

Bei der Analogen Signaturanalyse werden sichere Testsignale mit geringer Leistung an den Bauteil angelegt um "Impedanzsignaturen" am PC-Schirm zu erzeugen. Sämtliche Tests erfolgen im stromlosen Zustand der Baugruppe und somit völlig gefahrlos für Anwender und die getesteten Bauteile.

Es können Signaturbibliotheken von Gut-Mustern abgenommen und an weitere Servicezentren mit PFL-Systemen zum Vergleich anstelle von Referenzplatinen gesendet werden.. Die Signaturen von Gutmustern können rasch digitalisiert, untersucht, gespeichert und auf einer Vielzahl von Druckern ausgedruckt werden. Der PFL vergleicht automatisch die Signaturen von suspekten Bauteilen mit auf Festplatte gespeicherten Referenzen und druckt die Testergebnisse mit Gut- und Schlecht-Signaturen zum Vergleich

#### **Der Pulsgenerator**

Ein integrierter Pulsgenerator ermöglicht das Testen von Dreipolen wie z.B. Transistoren, Thyristoren und Triac's. Weitere Informationen finden Sie unter ASA Bauteiltests für Dreipole.

#### In Circuit Test

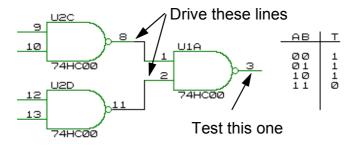

Beim In Circuit Test (ICT) vergleicht der PFL780 die logische Funktion eines Bauteils mit einem Modell des entsprechenden Bauteils in der Datenbank. Der PFL780 ist in der Lage die Funktion eines Bauteils in der Schaltung zu "lernen" und diese Konfiguration als Referenz zu verwenden. Logische High und Low "Guardspannungen" an den Frontplattenanschlüssen des PFL780 ermöglichen den isolierten Test von Busbausteinen.

### Anzeige von Verbindungen und logischen Fehlern

Die ICT-Software erkennt verbundene Pins und zeigt ein logisches Zeitdiagramm mit dem Status der Pins während des Tests.

### Die PFL Bauteilbibliothek

Die PFL Software beinhaltet eine umfangreiche Datenbank von integrierten Bausteinen welche in der Elektronikindustrie weithin eingesetzt werden.

### **Anwendungsgebiete**

Der PFL ist das ideale Instrument für einen breiten Anwendungsbereich:

Feldservice – Fehlersuche.

Produktion – Wareneingangstest/Fehlersuche.

Reparatur – rasche Diagnose.

### **PC-Steuerung**

Die PFL Software läuft auf einem IBM PC (oder Kompatiblen) Steuerrechner unter dem Windows 95 Betriebssystem. Befehle und Daten werden über eine schnelle serielle RS232-C-Verbindung zum Rechner übertragen.

Das Programm bietet eine integrierte Umgebung zum Schreiben von Testprogrammen, Akquirieren, Darstellen und Speichern von Signaturen sowie zur Überwachung der Systemsicherheit. Signaturen können sofort digitalisiert und als Referenz auf der Festplatte des Rechners für den Vergleich mit suspekten Bauteilen gespeichert werden.

Programme für den Bauteiltest können einfach erstellt, auf Festplatte gespeichert und auf Diskette zur Archivierung oder Weitergabe an Serviceorganisationen, Reparatur-zentren etc. abgelegt werden.

### Systemanforderungen

Bevor Sie die PFL Software installieren, überprüfen Sie ob der Steuerrechner die folgenden Voraussetzungen erfüllt:

Computer – IBM PC oder kompatibel

Prozessor – 80486 oder höher

Arbeitsspeicher – 16Mbytes RAM

Videokarte und Monitor – VGA Farbe

51/4" oder 31/2" Diskettenlaufwerk

20 Mbytes freier Speicher auf Festplatte

freie RS 232 C serielle Schnittstelle

Druckerschnittstelle

Betriebssystem – Microsoft  $^{\circledR}$  Windows 95

## Installation des Systems

### Auspacken

Das Gerät ist in einem stabilen Karton verpackt. Öffnen Sie diesen vorsichtig und entnehmen Sie das Gerät sowie das Zubehör. Bewahren Sie die Verpackung für eine eventuelle spätere Verwendung auf. Falls das Gerät auf irgend eine Weise beschädigt ist, verständigen Sie bitte Ihren POLAR-Distributor.

Der PFL Lieferumfang beinhaltet das Gerät sowie das Standardzubehör (angeführt unter Spezifikation)

**Zur Beachtung:** Falls das Gerät in kalter Umgebung geliefert oder gelagert wurde, so lassen Sie es vor Anschluß an das Netz die Umgebungstemperatur erreichen.

### Anschluß des PFL an die Netzversorgung

Prüfen Sie das Spannungsschild an der Rückseite des Geräts und vergleichen Sie diese mit der lokalen Netzspannung.

Falls die Spannungseinstellung nicht mit der Netzspannung übereinstimmt, so lassen Sie das Gerät von einem Fachmann auf die erforderliche Einstellung bringen. Anweisungen für die Änderung der Netzspannungseinstellung finden Sie im PFL Servicehandbuch.

Zur Beachtung: Falls ein spezieller Netzstecker an das Netzkabel montiert wird, so muß dies durch einen Fachmann erfolgen, wobei auf korrekten Anschluß der Schutzerde zu achten ist. Der abgezwickte Netzstecker muss sicher entsorgt werden.

Das Netzkabel verwendet folgende Farben:

Europe

Braun Phase

Blau Nulleiter

Grün/Gelb Schutzerde

Schließen Sie das Netzkabel and das Gerät und an die Steckdose (Der Netzschalter befindet sich auf der Geräterückseite unterhalb des Netzanschlusses ).

Wenn der Selbsttest nach dem Einschalten erfolgreich verläuft, so leuchtet die SYSTEM OK LED.

Eine blinkende SYSTEM OK LED zeigt an, daß einer oder mehrere Fehler während des Selbsttest aufgetreten sind. — Kontaktieren Sie in diesem Fall Ihren POLAR-Vertreter.

### Installation der PFL Software

Dem Anwender wird empfohlen, eine Arbeitskopie der PFL Installationsdisketten vor der Installation anzufertigen und die Originaldisketten sicher zu verwahren.

### Erstellen einer Arbeitskopie

Legen Sie die PFL Programmdiskette in das Laufwerk ein.

Doppelklick auf **Arbeitsplatz** und das Symbol für das Laufwerk mit der PFL-Diskette.

Wählen Sie aus dem Menü **Datei - Diskette kopieren**.

Klicken Sie **Quelldiskette** und **Zieldiskette** (Sie können für beide das gleiche Laufwerk wählen) und wählen Sie **Starten**

Wiederholen Sie diesen Vorgang für die weiteren Disketten.

Beide Disketten müssen gleiche Type sein. Daten auf der Zieldiskette werden gelöscht.

#### Installation des Programms

Schließen Sie alle anderen Programme.

Klick auf Start — Einstellungen.

Wählen Sie Systemsteuerung.

Doppelklick auf Software.

Unter Installieren/Deinstallieren klick auf Installieren.

Legen Sie die erste PFL Diskette in das Laufwerk ein und wählen Sie **Weiter**.

Nachdem **Setup.exe** in der Eingabezeile erscheint, wählen Sie **Weiter**.

Folgen Sie den weiteren Instruktionen.

Zur Vereinfachung kann eine Ikone auf den Arbeitsplatz kopiert oder durch Ziehen auf die Start-Schaltfläche erstellt werden (Siehe Einführung in Windows 95). Das Installationsprogramm erzeugt einen PFL-Ordner und Dateistruktur und kopiert die PFL-Dateien auf die Festplatte. Folgen Sie den Instruktionen auf dem Bildschirm um die Installation abzuschließen. Die Installation fügt den POLAR Fault Locator Ordner (zusammen mit den Programm-Ikonen) dem Programme Menü hinzu.

### Auswahl der PFL Gerätetype

Während des Installationsvorganges ist es notwendig, die Gerätetype des PFL (PFL760 oder PFL780) anzugeben. Wählen Sie PFL760 oder PFL780 aus.

Hinweis: Sie können die Gerätetype auch nach der Installation im Menü **Konfiguration** ändern.

Während des Installationsvorganges ist es weiters notwendig, die serielle Schnittstelle für die Verbindung zum PFL anzugeben. Wenn Sie nicht sicher sind, welche Schnittstelle verwendet wird, so lassen Sie die Defaulteinstellungen. Die Schnittstellenparameter werden automatisch durch die Software eingestellt.

Zur Beachtung: Sie können die Einstellung auch nach der Installation im Menü **Konfiguration** ändern.

### Anschluß des Computers an den PFL

PFL Befehle und Daten werden zwischen PFL und dem Steuerrechner über eine serielle Verbindung (RS232) mittels dem beigefügten Kabel übertragen

Vor Anschluß des Kabels sollten PFL und Computer ausgeschaltet sein.

Schließen Sie das Kabel an die serielle Schnittstelle des Rechners und des PFL (Geräterückseite) an. Schrauben Sie die Stecker fest. Schalten Sie den PFL und den Rechner ein.

Um die korrekte Funktion des Gerätes und die Einhaltung der EMV-Vorschriften sicherzustellen, ist es wichtig, das mitgelieferte Kabel zu verwenden.

### **Start des Programms**

Die Polar Fault Locator Ikone

Der PFL Schirm zeigt das zuletzt geöffnete Testprogramm Um das Programm zu starten, doppelklicken Sie auf die Polar Fault Locator Ikone - es öffnet der Hauptschirm.

Der PFL ruft das zuletzt geöffnete Programm auf (oder ein leeres Programm mit Namen **Unbenannt** falls noch keine Programmme erstellt wurden.

### **Der Hauptschirm**

Der Hauptschirm beinhaltet:

Das Hauptdisplayfenster

Die Menüleiste

Die Tool-Leiste

Die Ergebnisleiste

Die Statusleiste

Die Toolleiste und Ergebnisleiste können fixiert bleiben oder an eine beliebige Stelle gezogen werden - Klicken Sie auf die Leiste und ziehen Sie diese an den gewünschten Ort.

Bedienerfunktionen können durch Klicken der entsprechenden Schaltfläche auf der Toolleiste oder über das Menüsystem oder durch Bewegen der Markierung über die gewünschte Option und Drücken von <ENTER>.

### **Systemkonfiguration**

Das **Hilfsmittel**-Menü dient zur Einstellung der Betriebsumgebung. Im **Hilfsmittel**-Menü können Sie:

Paßwörter und Zugriffsrechte definieren

die serielle Schnittstelle wählen

Bauteilbibliotheken hinzufügen oder löschen

die Liste der installierten Bauteile durchsehen

die "Loop Compensation" - Routine starten, welche den Einfluß der Kapazitäten der Meßhardware auskalibriert.

Mit der Diagnose die Systemfunktionen prüfen

die Bildschirmfarben ändern

Benutzerhinweise des PFL aktivieren und deaktivieren

### Einstellung der PFL Steuersoftware

### **Systemsicherheit**

Der Hilfsmittel – Konfiguration Befehl ermöglicht dem Systembetreuer das Vergeben eines Paßworts um Programme oder Systemeinstellungen vor unbeabsichtigtem Löschen oder Verändern zu schützen.

Der PFL bietet zwei Sicherheitszustände: **Gesichert** und **Ungesichert**. Ist das System ungesichert so hat der Benutzer Zugriff auf alle Funktionen. Im gesicherten Zustand ist ein Ändern von Testprogrammen sowie der Zugriff auf die Parametereinstellungen, Systemkonfiguration und die Initialisierfunktion (um die Datenaufzeichnung zu Löschen) nicht möglich.

Wählt der Benutzer eine geschützte Funktion, so wird er zur Eingabe des Passwortes aufgefordert.

### Paßworteinstellung

Um ein Paßwort im Hilfsmittel-Menü einzugeben:

Wählen Sie den Konfiguration-Befehl.

Klicken Sie die **Passwort**-Box und geben Sie das neue Paßwort ein. Das neue Paßwort ersetzt das Alte. (falls vorhanden). WICHTIG: Notieren Sie das Paßwort.

Geben Sie im Feld **Bestätigung** das Paßwort erneut exakt wie im der **Passwort**-Feld ein. Die Auswahl **Passwortaktivierung beim Verlassen der Software** (defaultmäßig aktiviert) aktiviert den Paßwortschutz nach dem Schließen des **Konfiguration**-Dialogfensters. Deaktivieren dieser Box ermöglicht Zugriff auf alle Funktionen während dieser Sitzung — Der Paßwortschutz wird erst mit dem nächsten Start der Software aktiviert.

### Reduzierung der Akquisitionspriorität

Aktivieren Sie diese Einstellung wenn das Neuzeichnen der Signatur in der LIVE-Darstellung sehr langsam erfolgt. Dies ist möglicherweise auf langsameren PC's und/oder Grafikkarten der Fall. Auf ausreichend schnellen PC's sollte diese Funktion nicht aktiviert werden.

#### Benutzerhinweise einstellen

Die **Hinweise** - Registerkarte zeigt eine Liste von Systemhinweisen, welche je nach Erfordernis aktiviert und deaktiviert werden können.

So kann der Benutzer z.B. folgende Hinweise aktivieren und deaktivieren:

Das Baugruppenhinweise-Fenster beim Öffnen eines Testprogramms.

Systemhinweise wenn ein Test zu ungültigen Ergebnissen führen kann, z.B. wenn Vcc oder Gnd fehlt oder offene Pins erkannt wurden.

Der QuickStart-Dialog beim Starten der PFL Software.

Ist die **Tips mit Bauteilhinweisen**-Box aktiviert, so zeigt die PFL-Software einen Hinweis, wenn Signaturen eines Open-Kollektor oder Tristate-Bausteins aufgenommen werden sollen. Darin wird auf die Anwendung von Guard-Spannungen hingewiesen um Unstabilitäten zu vermeiden. Siehe *Isolieren von Bauteilen in der Schaltung*

### Ändern der Bildschirmfarben

Wählen Sie die **Farbeinstellungen**-Registerkarte um die aktuellen Farbeinstellungen anzuzeigen. Um eine Farbe zu ändern, klicken Sie auf den Namen des Bildschirmelements in der Dialogbox und anschließend auf die **Ändern**-Schaltfläche. Wählen Sie die neue Farbe aus der **Farbe**-Palette und klicken Sie auf **OK**.

Um eine neue Farbe zu definieren, wählen Sie die der Wunschfarbe ähnlichste, klicken Sie auf **Farben definieren**, klicken Sie auf die Farbmatrix und verändern Sie die Farbattribute mit dem Regler und klicken dann auf **Farbe hinzufügen**. Schließen Sie mit **OK** ab.

### **Schleifenkompensation**

Das PFL-System bietet die Möglichkeit, Kapazitäten der Hardware zu kompensieren.

Entfernen Sie dazu die Testclips von Bauteilen und wählen Sie im **Hilfsmittel**-Menu die Funktion **Schleifenkompensation**. Der PFL führt nun eine automatische Schleifenkompensation zum Ausgleich der Streukapazitäten durch.

### Diagnose

Die Wahl der **Diagnose**-Funktion zeigt das Hardwarediagnose-Dialogfenster. Durch Markieren der Klickboxen können einzelne Tests ein- und ausgeschaltet werden. Die Hardwarediagnose beinhaltet den Test der Kanal A und B Sicherung sowie der Sicherung der eingebauten 5V/5A Meßojektversorgung. Siehe *Servicieren des PFL* für Informationen zum Sicherungswechsel sowie für technische Unterstützung.

### Ausstieg aus der PFL-Software

Um die aktuelle Sitzung zu beenden, wählen Sie **Beenden** aus dem **Datei**-Menü.

## Allgemeine Beschreibung

### **Analoge Signaturanalyse**

Das PFL Fehlerdiagnosesystem testet Bauteile, indem ein strom-begrenztes Wechselspannungssignal an den Bauteil angelegt wird und dessen resultierende Strom-Spannungskennlinie auf dem Bildschirm dargestellt wird. Jeder Bauteil zeigt dabei eine eigene charakteristische Signatur, welche eine einfache Unterscheidung ermöglicht.

Die zwei Eingangskanäle A und B ermöglichen den Vergleich eines guten Referenzbauteils mit einem defekten Bauteil. Fehler können auf diese Weise selbst ohne genaue Kenntnis der Funktion einer komplexen Baugruppe festgestellt werden. Für Baugruppen ohne ausreichende Dokumentation in Form von Schaltplänen oder Servicehandbüchern ist dies besonders hilfreich.

#### **In-Circuit Test**

Mittels ICT (In-Circuit Test) bietet der PFL780 die Möglichkeit, die logische Funktion integrierter Bausteine zu testen. Dabei wird das Verhalten mit einem gleichartigen "idealen" IC aus einer umfangreichen Bibliothek an Bauteilen verglichen.

Die Datenbank des PFL780 enthält eine Vielzahl an integrierten Logikbausteinen (von verschiedenen Familien), von einfachen Gattern bis hin zu Prozessoren.

Der PFL780 kann das Verhalten eines Bausteines im eingebauten Zustand einer guten Platine "erlernen" und verwendet dieses als Referenz. Bauteilanschlüsse, die permanent auf Low oder High liegen bzw. Querverbindungen zwischen Anschlüssen werden dabei natürlich berücksichtigt.

Während des Programmier- und Testvorgangs werden die Pinverbindungen und die logischen Zustände angezeigt, um die Beziehungen zwischen Steuerleitungen und den Ein-/ Ausgängen anzuzeigen, um sie visuell begutachten zu können.

Sogenannte "Guard"-Spannungen (Logisch High und Low) auf der Frontplatte ermöglichen dem Anwender, Bauteile zu deaktivieren, die sich in der Nähe des zu testenden Bausteins befinden, um ihn ohne Demontage auch im isolierten Zustand zu überprüfen.

### Bedienungselemente und Anschlüsse

### Die PFL Frontplatte

Die Frontplatte besitzt Anschlüsse für:

Scannereingänge Kanal A und B (64 Pins / Kanal)

Prüfspitzen Kanal A und B

Zwei parallele Masseanschlußklemmen (COM)

Zwei parallele Pulsgeneratorausgänge

ICT 5V Spannungsversorgung (nur PFL780)

4 x ICT Logisch High (5V) und Low (0V) Guardspannungen (nur PFL780)

#### Scannerkanäle

Zur Beachtung: Vergessen Sie nicht die Masseverbindung Der PFL Scanner bietet die Möglichkeit des schnellen Erfassen von Signaturen auf allen Pins des zu testenden IC's. Der Signalweg wird durch die COM-Verbindung geschlossen.

### Kanal A und B Prüfspitzen

Der PFL wird mit einem Paar Prüfspitzen ähnlich denen eines Multimeters ausgeliefert, welche an die A und B Buchsen angeschlossen werden. Die Kanal A und B Prüfspitzen sind parallel zu den Scannereingängen geschaltet um Kontaktfehler am Testclip finden zu können.

Bei Verwendung des **LIVE**-Modus werden die Scannerkanäle isoliert und die Eingänge des PFL sind nur mit den Prüfspitzen verbunden.

### COM (Masse) Anschlüsse

Der PFL weist zwei parallele COM-Massebuchsen für die Verbindung zur Masse des Prüflings auf. Werden zwei Boards verglichen, so müssen die Massen *beider* Boards mit den COM Buchsen des PFL verbunden werden.

#### Pulsgenerator-Ausgänge

Der PFL bietet eine Pulsgeneratorschaltung welche es ermöglicht, das Leitverhalten von Transistoren, Thyristoren, Triacs und anderen Dreipolen zu untersuchen, indem Pegel, Pulsbreite, Polarität und Zeitverzögerung des Pulsausganges verändert werden können. Zwei Pulsausgänge dienen zum Vergleich zweier Boards.

Verbinden Sie die Pulsgeneratorleitungen mit den beiden blauen PULSE OUT-Buchsen am Anschlußpanel. Der Pulsgenerator erzeugt identische Signale auf beiden Buchsen gegen Masse. Die PULSE OUT-Signale werden über separate Verstärker gespeist, so daß bei einem Kurzschluß an einem Ausgang das Signal am zweiten Ausgang nicht beeinflußt wird.

### ICT 5V Stromversorgung

Verwenden Sie die PFL780 +5V ICT Stromversorgung um ein Board während des ICT zu versorgen. Die +5V ICT Versorgung ist nur während des ICT aktiv.

### ICT Guard-Spannungen

Der PFL780 bietet logische HIGH (5V) und LOW (0V) Guardspannungen um Busbausteine während des Tests zu isolieren. Bis zu 4 Guardspannungen können dabei an ausgewählte Bausteine zur Steuerung von Enable-Eingängen verwendet werden, um die Bauteile zu isolieren (um z.B. Bausteine zu deaktivieren, welche gemeinsame Daten- oder Adressleitungen mit dem Prüfling aufweisen).

#### Die PFL Rückwand

Auf der Gerätrückseite befinden sich der IEC Netzanschluß, Netzschalter, Fußpedalanschluß, RS232-Anschluß und die Prüfkanalsicherungen.

### Fußpedalanschluß

Verbinden Sie das POLAR Fußpedal (ACC124) mit dem Fußpedalanschluß auf der Geräterückseite. Betätigen des Pedals entspricht einem Klick der **Test**-Schaltfläche oder dem **Testen**-Befehl aus dem **Bauteil**-Menü.

#### RS232-Anschluß

Der RS232-Anschluß dient zur Übertragung von Befehlen und Daten zwischen PFL und dem Steuerrechner. Verwenden Sie hierfür nur das mitgelieferte Kabel (ACC126).

Stellen Sie sicher, daß der Steuerrechner und der PFL ausgeschaltet sind, bevor Sie das Kabel anschließen.

Verbinden Sie das Kabel mit der seriellen Schnittstelle des Rechners und mit dem RS232-Anschluß des PFL.

### Erste Schritte mit dem PFL

#### **Das Live-Instrument**

#### **Das Live-Instrument**

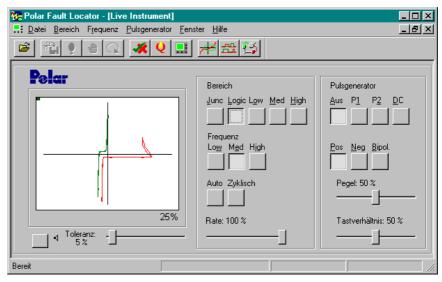

Das PFL **Live-Instrument** ermöglicht dem Benutzer Bauteile direkt mit der ASA-Technik zu testen und den Vergleich von Gut- und Schlechtboard durchzuführen.

Drücken Sie die **Live**-Schaltfläche — es erscheint der Live-Instrument Schirm wie unten abgebildet.

Bauteilsignaturen werden im Displayfenster auf dem Monitor des Steuerrechners dargestellt. Die Signaturen von Bauteilen auf Kanal A werden in Grün dargestellt, Kanal B-Signaturen in Rot.

Testmethoden für allgemeine Bauteile werden im Abschnitt ASA Bauteiltest detailliert behandelt.

### Verwendung der PFL Prüfspitzen

Der PFL wird mit einem Paar Prüfspitzen ähnlich denen eines Multimeters und Masseleitungen ausgeliefert, welche an die A und B Buchsen sowie an COM-Masse angeschlossen werden.

#### Anschluß der Prüfkabel

Verbinden Sie die rote Prüfspitze mit Kanal A, die schwarze Prüfspitze mit Kanal B und den schwarzen Testclip mit der COM-Buchse.

Verbinden Sie den COM-Testclip mit der Masse des Prüflings. Werden zwei Boards verglichen, so müssen die Massen beider Boards mit den COM Buchsen des PFL verbunden werden.

Verbinden Sie die A und B Prüfspitzen mit den Bauteilen auf den Boards. Verwenden Sie dabei Kanal A als Referenzkanal für das Gutmuster.

Doppelklick auf die Signatur zeigt eine Vollbildansicht - nochmaliger Doppelklick kehrt zur Normalansicht zurück.

### Einstellung der Prüfbedingungen

### **Testspannungswahl**

Das **Live-Instrument** ermöglicht die manuelle Wahl von Testbereichen und Frequenzen. Dadurch kann der Anwender die passende Spannung und Frequenz für den jeweiligen Bauteil vorgeben.

Um den Bereich oder die Frequenz zu wählen, klicken Sie auf die entsprechenden Schaltflächen oder wählen Sie mit der Tabulator-Taste Spannung, Frequenz und Pulsgenerator und verändern Sie die Einstellung mit der linken und rechten Cursortaste.

Es sollten nun die zwei Bauteilsignaturen am Display erscheinen, wobei Kanal A in Grün und Kanal B in Rot dargestellt wird.

### Wahl der Prüfspannung

Der PFL bietet eine Auswahl von strombegrenzten Prüfspannungen. Es kann jeweils nur eine Prüfspannung aktiv sein.

| Einstellung | Spannung                                    | Anwendung                                                                                                                                     |

|-------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|             |                                             |                                                                                                                                               |

| Junction    | 1V AC Spitze<br>500µA Strom-<br>begrenzung  | Halbleiterbauteile und<br>Schaltkreise, z.B.<br>Dioden, empfohlen für<br>IC's                                                                 |

| Logic       | 10V AC Spitze<br>5mA Strom-<br>begrenzung   | Geeignet für die<br>meisten Bauteile,<br>Ideal für Leucht-<br>dioden. Niedrige<br>Spannung und Strom<br>daher nur geringe<br>Bauteilbelastung |

| Low         | 10V AC Spitze<br>150mA Strom-<br>begrenzung | Niederohmige<br>Bauteile und<br>Leistungsdioden.<br>Nicht geeignet für<br>Kleinleistungsbauteile                                              |

| Med         | 20V AC Spitze<br>1mA Strom-<br>begrenzung   | Für Bauteile im mittleren Widerstands-bereich, Zenerdioden mit Durchbruch-spannungen bis 20V. Auch zum Prüfen von Diodenleckströmen.          |

| High        | 40V AC Spitze<br>1mA Strom-<br>begrenzung   | Hochohmige Bauteile,<br>Diodendurchbruch-<br>spannungen von 20V<br>bis 40V,<br>Diodenleckströme.                                              |

Wählen Sie mit der Maus oder mit rechter und linker Cursortaste die passendste Spannung um aussagekräftige Signaturen zu erzeugen. (Dies ist in der Regel die Spannung welche die größte Ablenkung ergibt.)

Durch die Auswahl höherer Testspannungen fließt mehr Strom, Signaturen mit besser erkennbaren Flanken werden angezeigt.

### Bereichssperre

Die Funktion **Bereichssperre** ermöglicht das Sperren einzelner Bereiche sodaß diese nicht durch manuelle Wahl, Zyklisch oder Auto aktiviert werden können.

### Wahl der Prüffrequenz

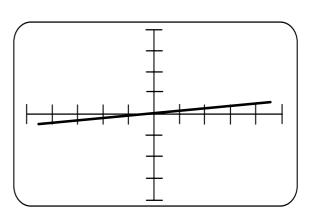

Die von einem reinen Widerstand erzeugte Signatur ist eine geneigt gerade Linie, deren Anstieg vom Widerstandswert abhängt. Für einen reinen Widerstand ist die gewählte Frequenz für die angezeigte Signatur unerheblich.

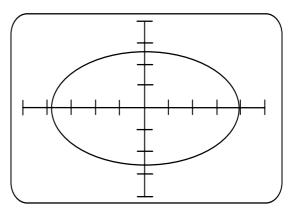

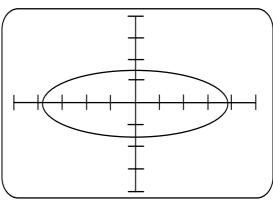

Durch die Wahl anderer Testfrequenzen kann sich die Impedanz des Bauteils ändern, das Widerstandsverhalten kann dadurch erhöht oder vermindert werden. Infolge der Energiespeichercharakteristik bewirken reaktive Bauteile eine Phasenverschiebung zwischen Strom und Spannung. Diese drückt sich als Kreis oder Ellipse, ausgerichtet mit dem Achsenkreuz, aus. Ist eine Widerstandskomponente in einer Schaltung gegenüber der Reaktanz dominierend, so wird die elliptische Signatur geneigt. Durch die Wahl verschiedener Testfrequenzen kann dieser Effekt minimiert oder maximiert werden. In einem Kondensator fließt bei höherer Frequenz mehr Strom; dies bewirkt eine größere Auslenkung in vertikaler Richtung. In einer Spule steigt der Stromfluß bei niederer Frequenz.

Siehe Abschnitt *ASA Bauteiltest* für eine Beschreibung von Halbleitersignaturen.

Die folgende Tabelle ist als Anleitung zur Frequenzwahl gedacht. Es kann jeweils nur eine Frequenzauswahl aktiv sein.

| Einstellung | Anwendung                                                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|

|             |                                                                                                                                 |

| Low         | 90Hz Signal für die Untersuchung<br>von Bauteilen mit größeren<br>Induktivitäten und Kapazitäten; z.B. in<br>Stromversorgungen. |

| Med         | 500Hz für die meisten Anwendungen der Fehlersuche.                                                                              |

| High        | 2KHz Signal für Bauteile und<br>Schaltungen mit kleinen Kapazitäten<br>und Induktivitäten.                                      |

**Hinweis:** Manche Schleifen auf Signaturen (infolge Streukapazitäten) können sogar auftreten, wenn die Prüfspitzen nicht mit dem Testobjekt verbunden sind, speziell in der Frequenzeinstellung **High**.

#### Auto

Der **Auto**-Befehl wählt automatisch den Bereich, der eine aussagekräftige Signatur ergibt. Kanal A dient hierbei als der steuernde Kanal. Um den **Auto**-Betrieb zu verlassen, wählen Sie manuell einen Testbereich oder **Zyklisch**.

### Zyklisch

Mit **Zyklisch** durchläuft das Gerät kontinuierlich jeden Spannungsbereich und zeigt die Signatur. Mit der **Rate**-Einstellung kann die Verweilzeit in den Bereichen eingestellt werden. Um **Zyklisch** zu verlassen, wählen Sie manuell einen Testbereich oder **Auto**.

#### Toleranz

Mit dem **Toleranz**-Regler (von 1 - 99%) ändern Sie die Empfindlichkeit des Signaturvergleichs als Prozentwert. Niedrigere Werte führen einen genaueren Vergleich durch, höhere Werte erlauben größere Unterschiede in den Signaturen. Als Anfangswert kann man z.B. mit 5% beginnen und dann die Empfindlichkeit so verändern, daß normale Toleranzen zulässig sind, echte Fehler jedoch erfaßt werden.

### Beepton

Klicken Sie auf die Beep-Schaltfläche um ein akustisches Signal bei Überschreitung des eingestellten Toleranzwertes zu geben. Diese Funktion ermöglicht dem Anwender Baugruppen zu vergleichen, ohne auf die Anzeige zu blicken.

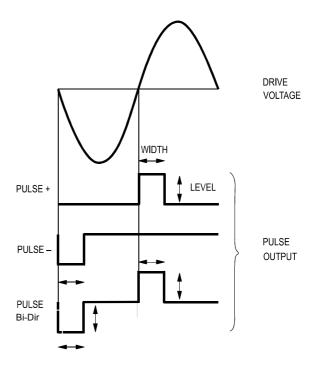

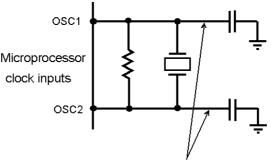

## Pulsgeneratorausgänge

Der PFL bietet eine Pulsgeneratorschaltung welche es ermöglicht, das Leitverhalten von Transistoren, Thyristoren, Triacs und anderen Dreipolen zu untersuchen, indem Pegel, Pulsbreite, Polarität und Zeitverzögerung des Pulsausganges verändert werden können.

Der Pulsgenerator erzeugt identische Signale auf beiden Buchsen gegen Masse. Die PULSE OUT-Signale werden über separate Verstärker gespeist, so daß bei einem Kurzschluß an einem Ausgang das Signal am zweiten Ausgang nicht beeinflußt wird.

#### Pulsgenerator-Anwendungen

Der Pulsgenerator ermöglicht die Durchführung verschiedener Tests an einer Vielzahl von Dreipolen. Der

Beep-Schaltfläche

- Verwenden Sie den

Beepton zur akustischen

Fehlersuche.

Pegel des Pulsers kann im **Live Instrument**-Betrieb durch Verschieben des Reglers mit der Maus oder durch Auswahl per Maus und mit den Cursortasten verändert werden.

Hinweis: der Pulgenerator wird abgeschaltet, wenn **Junction** gewählt wird.

Siehe *ASA Bauteiltest* für eine detaillierte Beschreibung des Dreipoltests.

Verbinden Sie die Pulsgeneratorleitungen mit den beiden blauen PULSE OUT-Buchsen an der Buchsenleiste.

# Die **Pulser**-Einstellungen werden in folgender Tabelle dargestellt:

| Pulstype       | Funktion                                                                                                                                                                                                                                    |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC Pos         | Wählt eine positive Gleichspannung. Die Spannung kann mit <b>Pegel</b> eingestellt werden.                                                                                                                                                  |

| DC Neg         | Wählt eine negative Gleichspannung. Die Spannung kann mit <b>Pegel</b> eingestellt werden.                                                                                                                                                  |

| P1             | Das Pulssignal P1 startet beim Nulldurchgang des Testsignals. Die Pulsbreite wird mit <b>Tastverhältnis</b> eingestellt, die Spannung mit <b>Pegel</b> .                                                                                    |

| P1 Pos         | Wählt ein positives Pulssignal wie in<br>Abbildung Puls 1 Ausgang                                                                                                                                                                           |

| P1 Neg         | Wählt ein negatives Pulssignal wie in Abbildung Puls 1 Ausgang                                                                                                                                                                              |

| P1 Bipol.      | Wählt ein bipolares Pulssignal wie in Puls 1<br>Ausgang, Pulsbreite wird mit <b>Tastverhältnis</b><br>und Pulsamplitude mit <b>Pegel</b> eingestellt.                                                                                       |

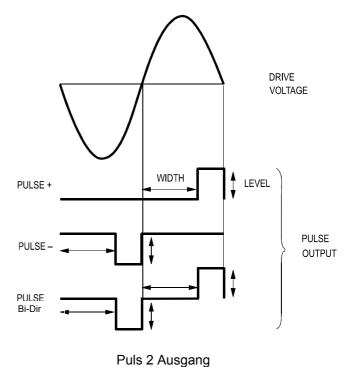

| P2             | Das Pulssignal P2 startet nach dem Nulldurchgang bei einem Punkt des Testsignals, welcher mit <b>Tastverhältnis</b> eingestellt wird. Es endet beim nächsten Nulldurchgang des Testsignals. Die Spannung wird mit <b>Pegel</b> eingestellt. |

| P2 Pos         | Wählt ein positives Pulssignal wie in Abbildung Puls 2 Ausgang                                                                                                                                                                              |

| P2 Neg         | Wählt ein negatives Pulssignal wie in<br>Abbildung Puls 2 Ausgang                                                                                                                                                                           |

| P2 Bipol.      | Wählt ein bipolares Pulssignal wie in Puls 2<br>Ausgang, Pulsbreite wird mit <b>Tastverhältnis</b><br>und Pulsamplitude mit <b>Pegel</b> eingestellt.                                                                                       |

| Tastverhältnis | Ändert die Pulsbreite bis zu einem Maximum der halben Periodendauer                                                                                                                                                                         |

| Pegel          | Ändert den Pulspegel zwischen 0 und 5V.                                                                                                                                                                                                     |

# Es kann jeweils nur eine Einstellung DC, Pulse1 oder Pulse 2 getroffen werden

Puls 1 Ausgang

## Test integrierter Schaltungen

Alle integrierten Schaltkreise können durch paarweises Abtasten der Anschlüsse getestet werden. Die meisten ICs zeigen eine Signatur ähnlich von Zenerdioden.

Bitte beachten Sie, daß ICs durch unterschiedliche Herstelltechnologie deutlich abweichende Signaturen zeigen können. Diese Tatsache muß berücksichtigt werden, bevor ein Bauteil als schlecht diagnostiziert wird.

Siehe *ASA Bauteiltests* für die Besprechung von IC-Tests - dieses Kapitel enthält typische IC-Signaturen.

Die COM-Strippe muß auf jedem Testobjekt mit einem gemeinsamen Punkt, normalerweise 0V, verbunden werden. Es kann auch nützlich sein, für die Signaturanalyse den Pin Vcc als gemeinsamen Punkt zu verwenden.

## **Bauteiltest mit Quicktest**

Die PFL780 **Quicktest**-Funktion ermöglicht dem Anwender der Vergleich zwischen Gut- und Schlechtboard ohne ein Testprogramm erstellen zu müssen. Wenn Gutmuster verfügbar sind, kann der Anwender ein Vergleichsverfahren zum Bauteiltest anwenden. **Quicktest** nimmt die Referenzsignaturen eines Gutmusters auf und vergleicht diese mit dem Prüfling.

Mittels **Quicktest** werden die Signaturen eines Gutmusters aufgenommen und mit dem Prüfling verglichen.

## Vergleichstests mit Quicktest

Die **Quicktest**-Vergleichsfunktion kann auf drei Arten verwendet werden):

Durch Eingabe der Bauteiltype (Bibliothek).

Durch die Auswahl **ASA**, wobei das Gerät automatisch die Anzahl der Pins erkennt und einen ASA-Test durchführt

Durch die Auswahl **Probe** oder einer POLAR SMD-Prüfspitze.

Die **Quicktest**-Vergleichsfunktion **Bibliothek** ermöglicht die Auswahl eines Bauteils aus einer Bibliothek, welche vordefinierte Parameter für die gängigsten Bauteile aufweist. Die vordefinierten Parameter sind für die meisten Applikationen passend. Die Testparameter (Spannungen, Frequenzen, etc.) können jedoch mit dem Befehl **Parametereinstellungen** aus dem Menü **Bauteil** verändert werden.

## ICT Verbindungen (nur PFL780)

ICT Verbindungen prüft auf kurzgeschlossene Anschlüsse bzw. Masse-/5V-Schlüsse mittels dem ICT Funktionsmodell. Ist kein ICT-Funktionsmodell für den Baustein vorhanden, so führt der PFL einen ASA Verbindungstest (siehe unten) durch.

## ASA Verbindungen

**ASA Verbindungen** identifiziert Anschlüsse welche einen Masseschluß aufweisen.

Hinweis: Es kann jeweils nur eine Art von Verbindungstest gewählt werden.

## Vergleichstest eines Bauteils mit Quicktest

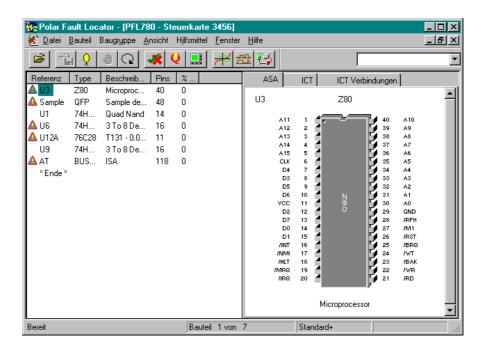

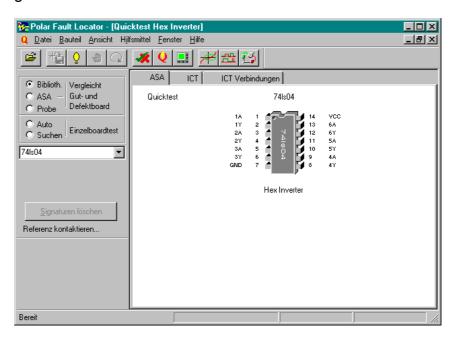

Klicken Sie die **Quicktest**-Schaltfläche — es erscheint der **Quicktest** Schirm (Bild unten PFL780) mit dem zuletzt getesteten Bauteil.

Im Vergleichstest zeigt **Quicktest** die Eingabeaufforderung **Referenz kontaktieren...** Geben Sie die Bauteiltype in der Referenzbox ein (z.B. durch Eintippen von 74LS244 oder durch Wahl von der Bauteilliste.).

Setzen Sie den Testclip auf den Bauteil auf und drücken Sie die **Test**-Schaltfläche oder drücken Sie den Fußtaster zum Aufnehmen und Speichern von Signaturen.

Klicken Sie die Test-Schaltfläche auf der Tool-Leiste um Signaturen

aufzunehmen und zu speichern.

(Wenn Kommentare oder spezielle Instruktionen (Siehe *Parametereinstellungen - Hinweis*) für diesen Bauteil

Die Ansichten können auch durch Doppelklick auf den dargestellten Bauteil gewählt werden. Um alle Ergebnisschirme anzuzeigen, wählen Sie Alle anordnen aus dem Fenster-Menü. Das Umschalten zwischen geöffneten Ansichten erfolgt ebenfalls im Fenster-Menü.

eingegeben wurden, so werden diese vor dem Aufnehmen der Signaturen angezeigt; zum Fortsetzen drücken Sie **OK**)

Die Referenzsignaturen können durch Umschalten in den Ansichtsmodus betrachtet werden. Klicken Sie die ASA Ansicht, ICT Ansicht oder Verbindungsansicht Schaltflächen um eine Ansicht zu öffnen oder zu wählen.

Es wird die Eingabeaufforderung **Prüfling kontaktieren...** angezeigt. Setzen Sie den Testclip auf den Bauteil auf und drücken Sie die **Test**-Schaltfläche - der Bauteil wird mit den gespeicherten Referenzsignaturen verglichen.

Es wird eine Meldung **Gut** oder **Fehler** in der Ergebnisleiste und eine grüner Haken oder ein rotes Kreuz auf den Registerkarten zur Markierung der einzelnen Tests angezeigt.

Die Referenz- und Prüflingssignaturen können durch Wahl des Ansichtsmodus angezeigt werden.

Nochmaliges Drücken von **Test** nimmt die Signaturen des Prüflings erneut auf und vergleicht sie mit der Referenz.

Ist ein neuer Bauteil zu testen, so können mit **Signaturen löschen** die Signaturen des Referenzbauteils und des Prüflings gelöscht werden.

#### Ansicht der ASA-Ergebnisse

Der ASA Ansichtsmodus zeigt typische ASA-Ergebnisse. Referenzsignaturen werden in Grün und Signaturen des Prüflings werden in Rot dargestellt.

Das ASA Ergebnisfenster zeigt die Referenzsignaturen für jeden Pin des geprüften Bauteils in allen gewählten Spannungsbereichen (Junction, Logic, Low, etc.)

ASA-Signaturen des Prüflings. Doppelklick auf eine Signatur zeigt eine Live-Darstellung des Pins.. Sie können auf andere Spannungsbereiche wählen indem Sie durch Klicken mit der rechten Maustaste ein Auswahlmenü einblenden Standardmäßig werden die ASA-Signaturen in absteigender Fehlergröße angezeigt, d.h. Signaturen mit der größten prozentuellen Abweichung werden in der oberen Reihe angezeigt. Mit den Scroll-Pfeilen auf der vertikalen Laufleiste können die weiteren Pins und Spannungsbereiche betrachtet werden.

Mit der rechten Maustaste wählen Sie **Ansicht nach Fehler**

Wählen Sie **Ansicht nach Anschlüssen** aus dem **Ansicht**-Menü um die Pins in aufsteigender Pinfolge in jedem Spannungsbereich anzuzeigen

Mit der Maximier-Schaltfläche schalten Sie auf Vollbilddarstellung.

## Ansicht der ICT-Ergebnisse

Die ICT-Ansicht zeigt das ICT-Logikdiagramm für den getesteten Bauteil.

Das Logikdiagramm ist eine diagrammatische Darstellung der logischen Funktionen des Bauteils in der Schaltung. Das Logikdiagramm zeigt die logischen Pegel jedes Pins in jedem Testschritt des Bauteils, wobei der Zusammenhang zwischen Steuerleitungen, Signalein- und ausgängen graphisch dargestellt wird.

ICT-Logikdiagramm

Das Logikdiagramm zeigt

den Status jedes Pins zu

jedem Testschritt. Mit den

Auf- und Ab-Cursortasten

können die weiteren Pins

zur Anzeige gebracht

werden.

Der PFL stellt die Referenzdaten des Bauteils in Grün dar. Die Logikpegel werden als High, Low und Tristate (strichlierte Linie zwischen High und Low) oder Don't Care (schraffierte Bereiche) gezeigt.

Fehlerhafte Pins werden Rot markiert. .

Durch Drücken der Leertaste oder durch Wahl von **Unbeschaltet** aus dem **Ansicht**-Menü können die logischen Funktionen des Bauteils in unbeschaltetem Zustand entsprechend dem Idealverhalten laut Bibliothek angezeigt werden.

## Ansicht von Verbindungen

Das **Verbindungsansicht**-Fenster zeigt die Ergebnisse des **Verbindungstest** für den Baustein. Der **Verbindungstest** zeigt:

Pins welche Stuck High der Stuck Low (d.h. mit fixen logischen Pegeln versehen sind)

Verbindungen zwischen Pins

Pins, welche als Stuck High (z.B. Vcc) erkannt wurden, werden durch eine Verbindung auf die Versorgungsschiene gekennzeichnet.

Pins, welche als Stuck Low (z.B. GND) erkannt wurden, werden durch eine Verbindung mit Masse gekennzeichnet.

Verbindungen, welche gleichermaßen auf der Referenz und auf dem Prüfling vorhanden sind, werden in Grün dargestellt. Unerwartete Verbindungen werden in Rot gezeigt, fehlende Verbindungen als strichlierte Linien.

## Einzelboardtest mit Quicktest (nur PFL780)

## Autokompensation

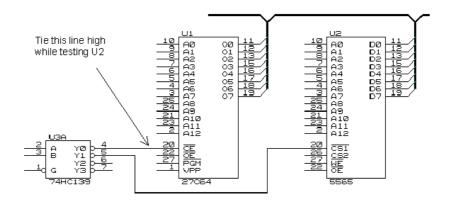

Steht kein Gutmuster für einen Vergleich zur Verfügung, so können Sie die **Auto**-Funktion zur Durchführung eines digitalen Funktionstests auf der Baugruppe verwenden.

Wenn ein Bauteil sich im eingebauten Zustand befindet, so kann sich sein logisches Verhalten von seinem unbeschaltetetem Zustand unterscheiden. So verhält sich z.B. ein Dual-NAND-Gatter mit beiden Eingängen verbunden wie ein Inverter. Die **Auto**-Funktion ist nun in der Lage dieses Verhalten zu kompensieren.

Wenn ein Bauteil mittels **Auto** getestet wird, so identifiziert der PFL780 verbundene Anschlüsse und Masse-/5V-Verbindungen und erstellt eine Softwaresimulation des Bauteils. Der Bauteil wird dann gegen dieses simulierte Softwaremodell im eingebauten Zustand getestet.

Wählen Sie Auto aus dem Einzelboardtest.

Kontaktieren Sie den Baustein, geben Sie die Bauteiltype ein und klicken Sie auf **Test**. Die Ergebnisse werden wie bereits beschrieben dargestellt.

Ist der PFL nicht in der Lage die Beschaltung des Bausteins automatisch zu kompensieren, so zeigt Quicktest einen Hinweis, daß gegen das Bibliotheksmodell getestet wird.

Ist der Baustein außerhalb der Schaltung zu testen, so aktivieren Sie die Klickbox **Test außerhalb der Schaltung**.

## Suchen nach Bausteintypen (nur PFL780)

Mit der Funktion **Suchen** können unbekannte Bausteine identifiziert werden (wenn z.B. die Beschriftung entfernt wurde oder schlecht lesbar ist). Der PFL780 sucht in der ICT Datenbank nach Bausteinen, welche gleiches logisches Verhalten aufweisen.

Bausteine mit gleichem Funktionsmuster werden im Suchtextfeld aufgelistet..

Ist der Baustein außerhalb der Schaltung zu testen, so aktivieren Sie die Klickbox **Test außerhalb der Schaltung**.

# **Asa Bauteiltest**

## Signaturformen

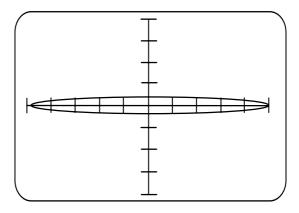

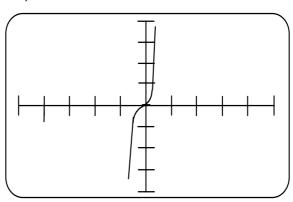

Bei der Analogen Signaturanalyse werden sichere, extrem leistungsarme Spannungen auf verschiedene Punkte einer Schaltung gelegt, die sogenannte "Impedanzsignaturen" auf dem PC-Bildschirm erzeugen.

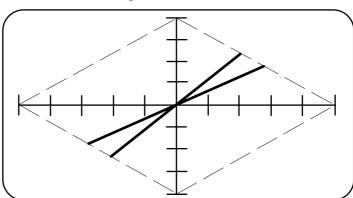

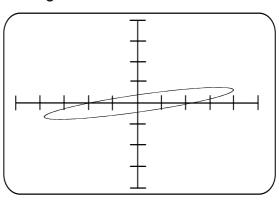

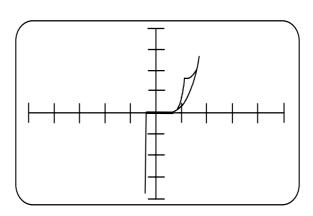

Der schnellste Weg der Diagnose ist der Vergleich von Signaturen. Meist ist keine detaillierte Analyse der Signaturform erforderlich.. Impedanzsignaturen sind Kurven, in denen der Strom über der Spannung aufgetragen wird. Die Skalierung hat ihren Ursprung in der Mitte des Schirms.

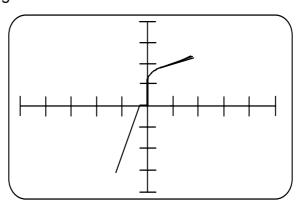

Positive Spannungen und Ströme werden im oberen rechten Quadranten des Bildschirms dargestellt, negative Spannungen und Ströme im unteren linken Quadranten (siehe Bild unten).

Alle Signaturen befinden sich innerhalb des rautenförmigen Feldes, welches durch die "Lastkurven", die die Endpunkte der Achsen verbinden, gebildet wird.

Anzeige X- und Y-Achse

Die Tabelle unten zeigt die Spitzenspannung und den maximalen Strom in jedem einzelnen Spannungsbereich:

| Bereich  | Spitzenspannung | Spitzenstrom |  |

|----------|-----------------|--------------|--|

|          |                 |              |  |

| Junction | 1V              | 500μA        |  |

| Logic    | 10V             | 5mA          |  |

| Low      | 10V             | 150mA        |  |

| Med      | 20V             | 1mA          |  |

| High     | 40V             | 1mA          |  |

PFL Spannungsbereiche

## **Test passiver Bauteile mit ASA**

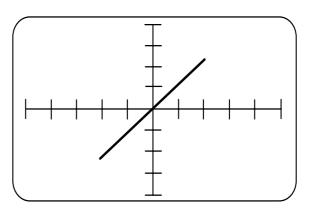

#### Test von Widerständen

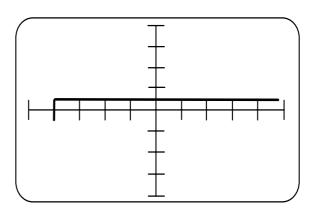

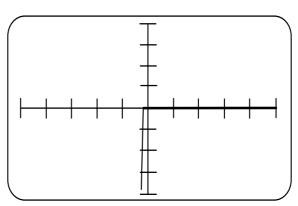

Die Signatur, welche von einem reinen Widerstand erzeugt wird, ist eine gerade Linie, deren Neigung vom Widerstandswert abhängt. Ein großer Widerstand bewirkt nur einen geringen Stromfluß, wenn eine geringe Testspannung angelegt wird. Die resultierende Signatur ist nicht einfach von einem Leerlauf zu unterscheiden. Durch die Wahl des Spannungsbereiches **High** fließt ein größerer Strom, und eine leichter erkennbare Signatur ist das Ergebnis.

Die Tabelle zeigt die Bereiche mit den ungefähren Widerstandswerten, in denen eine einfache Unterscheidung von einem Kurzschluß (vertikale Linie) und einem Leerlauf (horizontale Linie) möglich ist.

| Bereich  | Widerstandswert (Ohm) |  |

|----------|-----------------------|--|

|          |                       |  |

| Junction | 1K to 50K             |  |

| Logic    | 300R to 6K            |  |

| Low      | 16.5R to 300R         |  |

| Med      | 5K to 60K             |  |

| High     | 12K to 150K           |  |

Widerstandsbereiche

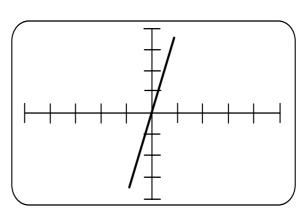

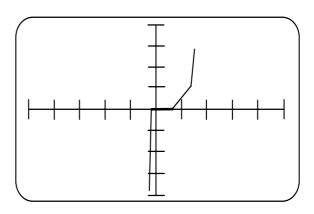

Die folgenden Abbildungen zeigen typische Signaturen für drei Widerstandswerte.  $2k\Omega$ ,  $270k\Omega$  and  $10K\Omega$ .

2K Widerstand **Logic** Bereich **Low** Frequenz.

270K Widerstand **High** Bereich **Low** Frequenz

10K Widerstand **High** Bereich **Low** Frequenz

#### Test von Kondensatoren

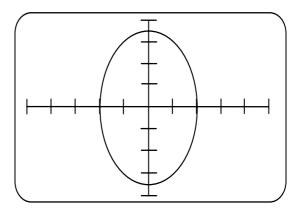

Aufgrund ihrer energiespeichernden Eigenschaft verursachen Reaktanzen eine Phasenverschiebung zwischen Spannung und Strom.

Dies wird durch eine kreisförmige oder elliptische Signatur dargestellt. Die folgenden Abbildungen zeigen typische Signaturen von drei Kondensatoren.

Bei einem rein kapazitiven Verhalten sind die Achsen der Ellipse mit den Achsen des Bildschirmes parallel. Ist jedoch auch eine ohmsche Komponente enthalten, so sind die Achsen der Ellipse gegenüber den Bilschirmachsen geneigt.

22uF Kondensator Low Bereich Low Frequenz

10uF Kondensator Low Bereich Low Frequenz

82pF Kondensator **High** Bereich **High** Frequenz

Die folgende Abbildungen zeigen die Signatur eines defekten 47µF Kondensators mit einem Widerstand-sverhalten sowie die Signatur eines guten 47µF Kondensators. Durch die Wahl unterschiedlicher Testfrequenzen kann die Impedanz verändert werden und der Einfluß der ohmschen Komponente vergrößert oder verkleinert sich.

47uF Kondensator **Low** Bereich **Low** Frequenz Defekter Kondensator mit ohmschen Anteil

47uF Kondensator Low Bereich Low Frequenz Guter Bauteil

Die folgende Tabelle zeigt die Bereiche von Kondensatoren mit den zugehörigen Frequenzen und Spannungsbereichen.

|         |              | Frequenz   |              |

|---------|--------------|------------|--------------|

| Bereich | Low          | Med        | High         |

| Bereien | Low          | Mica       | riigii       |

| Logic   | 300nF – 6uF  | 56nF – 1uF | 15nF – 300nF |

| Low     | 6uF – 100uF  | 1uF – 20uF | 300nF – 5uF  |

| Med     | 30nF – 300nF | 5nF – 68nF | 1.5nF – 15nF |

| High    | 10nF – 150nF | 2nF – 30nF | 500pF – 7nF  |

Kapazitätsbereiche

#### Test von Induktivitäten

Die folgende Tabelle zeigt die Bereiche von Induktivitäten mit den zugehörigen Frequenzen und Spannungsbereichen.

|         |              | Frequenz    |              |

|---------|--------------|-------------|--------------|

| Bereich | Low          | Med         | High         |

| Logic   | 500mH – 11H  | 100mH – 2H  | 25mH – 500mH |

| Low     | 30mH – 500mH | 6mH – 100mH | 1.5mH – 25mH |

| Med     | 10H – 110H   | 2H – 10H    | 500mH – 5H   |

| High    | 20H – 300H   | 4H – 50H    | 1H – 12H     |

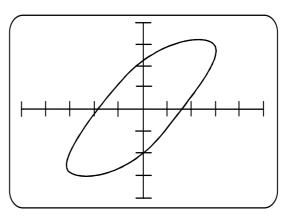

Die folgende Abbildung zeigt die Signatur einer Primärseite eines Ferrittransformators mit Testspannung **Low** und Testfrequenz **High**. Dies demonstriert den Effekt eines ohmschen Widerstandes, welcher die Neigung der Ellipse bewirkt.

Ferrittransformators Primärseite Low Bereich High Frequenz

Die folgende Abbildung zeigt einen ähnlichen (defekten) Transformator mit einer kurzgeschlossenen Windung. Der Bediener kann die passendste Testfrequenz — Low, Med und High (siehe Parametereinstellung) wählen. Durch einen Kondensator fließt mehr Strom bei höheren Frequenzen, welches durch eine größere vertikale Ablenkung dargestellt wird. Durch eine Spule fließt höherer Strom bei niedrigeren Frequenzen.

Ferrittransformator Primärseite **Low** Bereich **High** Frequenz Kurzgeschlossene Windung

## **ASA Test von Halbleitern**

## Test von Dioden, LEDs und Zenerdioden

In Vorwärtsrichtung zeigt eine Diode einen niedrigen Widerstand und einen Spannungsabfall von ca. 0.6 V. Dies produziert eine Signatur mit einer nahezu vertikalen Linie an der Y-Achse - siehe Diagramm unten.

Kleinsignaldiode **Logic** Bereich **Low** Frequenz

In Sperrichtung zeigt die Diode einen hohen Widerstand ähnlich einem Leerlauf-verhalten. Dies ergibt eine horizontale Linie nahe der X-Achse. Eine Leuchtdiode (LED) zeigt eine ähnliche Signatur wie eine konventionelle Diode mit Ausnahme, daß der Spannungsabfall in Sperrichtung ca. 1.5 V beträgt.

Eine Zenerdiode zeigt die selbe Signatur wie eine konventionelle Diode für Spannungen unterhalb der Zenerspannung. Wenn die Spannung in Sperrichtung die Zenerspannung erreicht, wird die Signatur eines geringen Widerstandes gezeigt. Die Abbildung unten zeigt die Signatur einer 8.2V Zenerdiode.

8.2V Zenerdiode **Med** Bereich **Low** Frequenz

Beim Test von Zenerdioden kann die Skalierung der X-Achse dazu verwendet werden, um die Zenerspannung zu messen. (Siehe Tabelle PFL Testspannungen).

Passende Spannungsbereiche sind:

Leistungsdioden Low

Kleinsignaldioden und LED's Logic

Zenerdioden Med bis zu 20V

High über 20V

HINWEIS: Die Signaturen sind invertiert, wenn die Prüfspitzen und COM-Verbindungen verpolt sind.

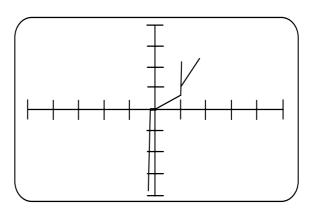

#### **Test von Transistoren**

Ein Transistor enthält zwei Halbleiterübergänge, welche aneinandergefügt sind (einer zwischen Basis und Kollektor, einer zwischen Basis und Emitter). Die Abbildungen unten zeigen typische Signaturen eines NPN Transistors (Basis-Emitter, Basis-Kollektor und Emitter-Kollektor) bei dem Kollektor und Emitter N-Type und die Basis P-Type ist.

NPN Transistor Basis-Emitter **Med** Bereich **Low** Frequenz

NPN Transistor Basis-Kollektor **Med** Bereich **Low** Frequenz

NPN Transistor Emitter-Kollektor **Med** Bereich **Low** Frequenz

Die Basis-Emitter Signatur ist ähnlich einer Zenerdiode. Hochfrequenz-Kleinsignaltransistoren sollten in diesem Modus nicht über längere Zeit betrieben werden! Andauernder Revers-Durchbruch des Basis-Emitterübergangs kann eine permanente Veränderung der Bauteilcharakteristik zur Folge haben. Siehe "Funktionstests" für eine Methode, die den Basis-Emitterübergang nicht im Revers-Durchbruch betreibt.

Die Basis-Kollektor Signatur ist ähnlich einer konventionellen Diode.

Die Kollektor-Emitter Signatur ist ähnlich einer Diode in Serie mit einer Zenerdiode. Wenn das Prüfsignal positiv ist (Rechter Quadrant), so ist der Kollektor-Basisübergang in Sperrichtung und der Basis-Emitterübergang in Durchlaßrichtung. Der Kollektor-Emitterübergang in Sperrichtung verhindert einen Stromfluß, was eine Leerlaufsignatur zur Folge hat (Horizontale Linie).

Wenn das Prüfsignal negativ ist (Linker Quadrant), so ist der Kollektor-Basisübergang in Durchlaßrichtung und der Basis-Emitterübergang in Sperrichtung. Basis-Emitter zeigen einen Zenerdurchbruch wie oben beschrieben, was eine Signatur mit einem Zener-Ende zur Folge hat. Siehe obige Warnung über den Betrieb des Transistors mit dem Basis-Emitterübergang in Sperrichtung.

Die Signaturen eines PNP-Transistors sind spiegelbildlich zu denen eines NPN-Transistors.

## Bestimmen der Transistoranschlüsse

Die Anschlüsse eines unbekannten Transistors können wie folgt identifiziert werden:

Wählen Sie den Bereich **Logic** und die Frequenz **Low**. Verbinden Sie den COM-Clip mit einem Anschluß des Transistors und prüfen Sie die anderen zwei Anschlüsse mit

der Prüfspitze für eine Übereinstimmung mit den Signaturen wie jene des NPN Transistors. (Siehe Test von Transistoren) Wenn die Signaturen Spiegelbilder der gezeigten sind, so handelt es sich um einen PNP-Bauteil.

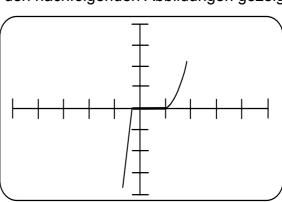

#### Funktionstest von Transistoren

Durch Ansteuern der Basis kann ein Funktionstest an Transistoren durchgeführt werden. Damit wird die Steuerwirkung der Basis überprüft.

Die folgende Prozedur gilt für einen NPN-Transistor. Der aussagekräftige Teil der Signatur befindet sich im oberen rechten Quadranten; Ignorieren sie den unteren linken Quadranten. Die Prozedur ist , falls nicht anders angeben, identisch für PNP-Transistoren, wobei die Anzeigen aber spiegelbildlich erfolgen (d.h. der wichtige Teil der Signatur erscheint im unteren linken Quadranten):

Verbinden Sie den Kollektor mit Kanal A, den Emitter mit COM und die Basis mit einem der beiden Pulsausgänge.

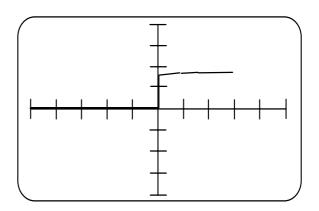

Wählen Sie den **Logic**-Bereich, **Low** Frequenz, **DC Pos** (für NPN) oder **DC Neg** (für PNP). Stellen Sie **Pegel** auf 0.

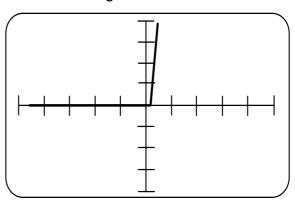

Die Signatur im rechten Quadranten ist eine horizontale Linie, es erfolgt kein Stromfluß. Wird **Pegel** erhöht, so wird der Basis-Emitterübergang leitend und der Transistor beginnt zu leiten. Dies erzeugt eine Signatur wie in folgender Abbildung.

Die Signatur ist ähnlich jener, die mit einem konventionellen Curve-Tracer erzeugt werden, mit Ausnahme, daß nur eine einzige Kurve erscheint. Ein weiteres Erhöhen von **Pegel** führt zur Sättigung des Transistors, was eine vertikale Linie nahe der Y-Achse ergibt.

NPN Transistor

Low Bereich

Low Frequenz

Kollektor-Emitter

DC Neg auf Basis

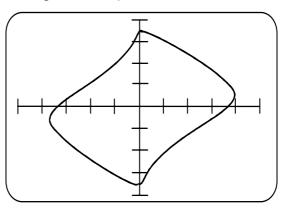

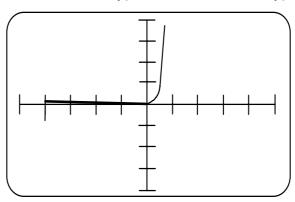

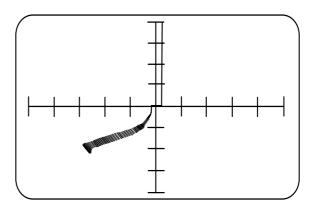

Da der Transistor als Schalter betrieben wird, sieht man am Beginn des Leitzustandes eine Signatur wie in Abbildung unten (welche umgekehrt ist, da sie für einen PNP-Transistor gilt.)

Das bedeutet keinen Fehler, aber zeigt den Bauteil im Schaltbetrieb zwischen normalem Leitzustand und Sättigung. Eine stabilere Anzeige erhält man, indem man einen anderen Spannungsbereich wählt.

PNP Transistor

Logic Bereich

Med Frequenz

Kollektor-Emitter

Pulse1 Neg

auf Basis

Die Wahl des Signals **Puls 1 Pos** vom Pulsgenerator zeigt Signaturen sowohl im Leitzustand als auch im Sperrzustand. Lassen Sie **Pegel** unverändert vom vorigen Schritt und verändern Sie die Pulsbreite mit **Tastverhältnis**. Ist der Puls HIGH, so ist der Basis-Emitterübergang im Leitzustand und der Transistor leitet. Ist der Puls LOW, sperrt der Transistor, und die Signatur zeigt einen Leerlauf.

## **Test von Junction Field Effect Transistors (JFETs)**

Der JFET besteht aus einem Halbleiterblock (dem Kanal) und einer Region, die mit Halbleitermaterial der entgegengesetzten Type zum Kanal (dem Gate) dotiert ist. Das Gate formt einen Diodenübergang mit jedem Ende des Kanals (dem "Source" und "Drain"), welcher wie konventionelle Dioden getestet werden kann.

Die Signaturen zwischen Source und Drain (siehe Funktionstests von Junction FET's) zeigen einen Widerstand mit niedrigem Wert und nichtlinearem Verhalten. Um eine stabile Anzeige zu erhalten, ist es notwendig, das Gate mit Source zu verbinden. Ein offenes Gate ist äußerst empfindlich gegen Interferenzen vom Testsignal.

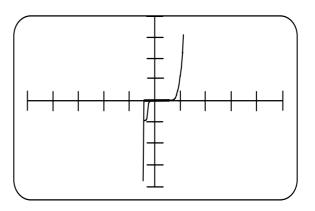

#### Funktionstests von Junction FET's

Der Leitzustand zwischen Source und Drain eines JFETs wird durch Reverse-Betrieb des Gate-Source-Überganges gesteuert.

Die folgende Prozedur gilt für N-Kanal FETs.

Der aussagekräftige Teil der Signatur erscheint im rechten Quadranten der Anzeige; ignorieren Sie den linken Quadranten. Die Prozedur ist, falls nicht anders angegeben, identisch für P-Kanal FETs, wobei eine spiegelbildliche Darstellung erfolgt (d.h. der wichtige Teil der Signatur erscheint im linken Quadranten)::

Verbinden Sie Drain mit Kanal A, Source mit COM und das Gate mit einem der beiden Pulsgeneratorausgänge.

Wählen Sie den **Logic** Bereich, **Low** Frequenz, **DC Pos** (für P- Kanal) oder **DC Neg** (für N-Kanal). Stellen Sie **Pegel** auf 0.

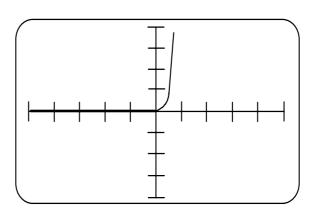

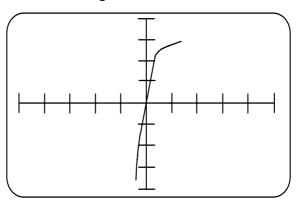

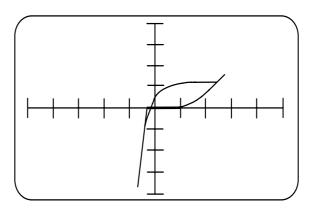

Wenn **Pegel** 0 ist, so ist die Drain-Source Signatur ähnlich wie in Abbildung unten. Wird **Pegel** erhöht (erhöhen der Revers-Vorspannung des Gate-Source-Übergangs), so wird der Leitzustand im Kanal reduziert. Wenn **Pegel** weiter erhöht wird, bricht der Leitzustand ab, und die Signatur im rechten Quadranten ergibt eine horizontale Linie.

Junction FET

Logic Bereich

Low Frequenz

Drain-Source

DC Pos

an Basis

## **Test von MOSFETs**

VORSICHT: Beachten Sie Antistatikvorkehrungen bei der Handhabung von MOSFETs. Verwenden Sie den **Logic** Bereich zum Testen (oder **Low** für Leistungs-MOSFETs). Verwenden Sie nicht die Bereiche **Med** oder **High**.

MOSFETs sind Feldeffekttransistoren, deren Gate vom Kanal isoliert ist. Gate-Drain und Gate-Source Tests zeigen normalerweise eine Leerlaufsignatur, jedoch besitzen einige MOSFETs eine Schutzdiode zwischen Gate und Source . In diesen Fällen zeigt die Signatur das Verhalten einer Zenerdiode

Wie beim JFET wird das Source-Drain Leitverhalten durch die Gate-Source Spannung bestimmt. MOSFETs sind in zwei Varianten - den Anreicherungstypen und den Verarmungstypen - erhältlich, wobei das Leitverhalten durch Vorwärts/Revers-Vorspannung des Gate-Source Überganges kontrolliert wird.

#### Funktionstests von MOSFETs

Folgen Sie dieser Prozedur für einen N-Kanal Anreicherungstyp. Der aussagekräftige Teil der Signatur erscheint im rechten Quadranten des Bildschirms. Ignorieren Sie den unteren linken Quadranten. Wenn nicht anders angegeben, gilt diese Prozedur auch für P-Kanal FETs. Die Signaturen sind spiegelbildlich (der wichtige Teil der Signatur erscheint im linken Quadranten):

Verbinden Sie Drain mit Kanal A, Source mit COM und das Gate mit einem der Pulsgeneratorausgänge

Wählen Sie den **Logic** Bereich, **Low** Frequenz, **DC Pos** (siehe Hinweis unten). Stellen Sie **Pegel** auf 0.

Hinweis: Um die erforderliche Polarität für die Gate-Ansteuerung zu bestimmen, beachten Sie, daß das Gate für Anreicherungstypen in Vorwärtsrichtung vorgespannt und für Verarmungstypen in Sperrichtung vorgespannt ist. N-Kanal Anreicherungstypen und P-Kanal Verarmungstypen erfordern eine positive Gatespannung, N-Kanal Verarmungstypen und P-Kanal Anreicherungstypen erfordern eine negative Gatespannung..

Wenn **Pegel** auf 0 gestellt ist, zeigt die Drain-Source Signatur eine horizontale Linie für Sperrverhalten. Wird **Pegel** erhöht (erhöhen der Vorwärts-Vorspannung des Gate-Source Überganges), wird die Leitfähigkeit des Kanals erhöht und eine Signatur wie die des JFET's gezeigt. Wird **Pegel** weiter erhöht, erhöht sich die Leitfähigkeit, bis zur Signatur eines kleinen Widerstandes (fast vertikale Linie).

## Test von Spezialbauteilen

## Test von Optokopplern

Ein Optokoppler besteht aus einer Eingangsdiode und einem elektrisch isolierten Ausgangstransistor (meist ohne angeschlossene Basis).