# **PCB Layer Calculation and Documentation Tool**

**User Guide**

# Speedstack PCB Stackup Design and Documentation

**Polar Instruments Ltd**

Polar Instruments Ltd.

Garenne Park St. Sampson Guernsey Channel Islands

GY2 4AF

**ENGLAND**

email: polarcare@polarinstruments.com

https://www.polarinstruments.com

MAN 199-2006

# **Speedstack User Guide**

#### POLAR INSTRUMENTS LTD

#### **COPYRIGHT**

Copyright 2020 © by Polar Instruments Ltd. All rights reserved. This software and accompanying documentation is the property of Polar Instruments Ltd and is licensed to the end user by Polar Instruments Ltd or its authorized agents. The use, copying, and distribution of this software is restricted by the terms of the license agreement.

Due care was exercised in the preparation of this document and accompanying software. Polar Instruments Ltd. shall not be liable for errors contained herein or for incidental or consequential damages in connection with furnishing, performance, or use of this material.

Polar Instruments Ltd makes no warranties, either expressed or implied, with respect to the software described in this manual, its quality, performance, merchantability, or fitness for any particular purpose.

#### **DISCLAIMER**

#### 1. Disclaimer of Warranties

POLAR MAKES NO OTHER WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, REGARDING PRODUCTS. ALL OTHER WARRANTIES AS TO THE QUALITY, CONDITION, MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT ARE EXPRESSLY DISCLAIMED.

# 2. Limitation of Liability.

POLAR SHALL NOT BE RESPONSIBLE FOR DIRECT DAMAGES IN EXCESS OF THE PURCHASE PRICE PAID BY THE END USER OR FOR ANY SPECIAL, CONSEQUENTIAL, INCIDENTAL, OR PUNITIVE DAMAGE, INCLUDING, BUT NOT LIMITED TO, LOSS OF PROFITS OR DAMAGES TO BUSINESS OR BUSINESS RELATIONS, WHETHER OR NOT ADVISED IN ADVANCE OF THE POSSIBILITY OF SUCH DAMAGES, THE FOREGOING LIMITATIONS SHALL APPLY, NOTWITHSTANDING THE FAILURE OF ANY EXCLUSIVE REMEDIES.

#### **TRADEMARKS**

Copyright Polar Instruments Ltd. © 2020

Microsoft<sup>®</sup>, Microsoft Windows<sup>®</sup>, Windows 7<sup>®</sup>, Windows 8<sup>®</sup>, Windows 10<sup>®</sup> and Microsoft<sup>®</sup> Excel<sup>®</sup> are registered trademarks of Microsoft Corporation.

IBM® is the registered trademark of International Business Machines Corporation.

All other trademarks acknowledged.

# **Speedstack specifications**

Maximum layer count 128+

Via rules Conventional, blind and buried

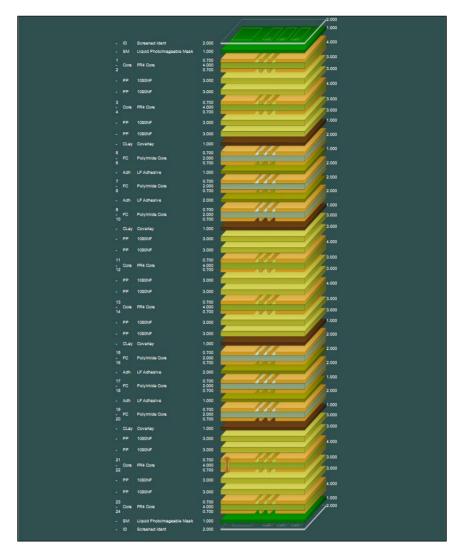

Materials library Foils, Cores, RCC foils, Non-copper cores, Prepregs,

Solder masks, Flexible cores, Bondply, Adhesive,

Coverlays, Ident inks, Peelable masks

Post press compensation Yes (user defined)

Finished thickness compensation Copper coverage/simple percentage

Stackup calculation Copper thickness, stackup thickness, dielectric

thickness, solder mask thickness

Drill types Mechanical, Laser, Laser stacked, Through plated

Drill-via fill types Copper, Resin, Solder Mask, Non-Conductive,

Conductive, Sintering Paste, Copper Paste

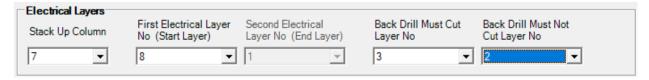

Back Drill Must Cut Layer No, Back Drill Must Not

Cut Layer No, Back Drill Minimum Distance From Cut Layer, Back Drill Maximum Distance From Cut

Layer, Primary Drill Size

Design rules check Design logic, symmetry, copper balance, board

thickness, manufacturing tests, resin starvation

Si8000m/Si9000e integration Bi-directional copy/paste structure parameters

Flex-rigid modelling Mesh/crosshatch ground plane modelling in

conjunction with Polar Si8000m/Si9000e

Controlled impedance structures 100+ structures supported with impedance goal

seeking and structure validation

Symmetrical stacks Structure mirroring for symmetrical stacks

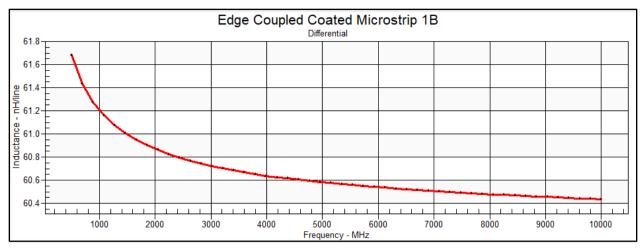

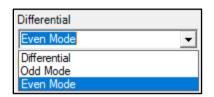

Loss/Frequency dependent Differential, Odd mode, Even mode graphed over a

modelling/graphing user-specifiable frequency range

Frequency dependent calculations Single frequency Er causal modelling using

(causal interpolation of dielectric interpolation of Er v frequency employing Svensson-

constant) Djordjevic method

Result presentation Length of line, Inches, Metres

Display series All Losses, Impedance Magnitude, Inductance,

Resistance, Capacitance, Conductance, Alpha, Beta

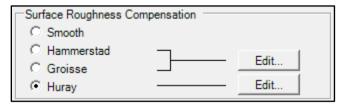

Surface roughness compensation Smooth, Hammerstad, Groisse, Huray, Cannonball-

Huray

Material library On-line and on-premises

File import IPC-2581 Rev B, Ucamco Job file, Ucamco

Integr8tor and Ucam (.ssx), XML, Zuken CR-8000

File export CGen Coupon Generator, CITS File, DXF, Gerber,

Stackup Image (JPEG, BMP, TIFF), Cadence Allegro (IPC-2581 Rev B), CSV, IPC-2581 Rev B, Mentor Graphics, XML file, Zuken CR-8000, Zuken DFM Center, Ucamco Integr8tor and Ucam (.ssx),

# Personal computer requirements

Computer IBM PC compatible

Processor Pentium 1GHz or better

Operating system Windows 10 or later

Environment Requires .NET Framework v2.0 or above

System memory required 2GB recommended

Hard disk space required 200MB (min.)

Video standard FHD (1920 x 1080\*)

2 FHD (1920 x 1080\*) monitors recommended

\* Note: refers to effective resolution (some

systems automatically apply scaling to render text readable – i.e. *effective resolution* refers to the

screen resolution after scaling.)

Licensing Electronic: local FlexNet license

Fixed: Parallel/USB key Floating FlexNet license (Windows servers only)

# Guide to the manual

Introduction Introduces Polar Instruments Speedstack.

Getting started with

Speedstack

Steps through the process of creating a simple stack

from a set of manufacturer's data.

Configuring Speedstack Setting up the Speedstack environment including

license options, crosshatch and structure defaults, goal

seeking parameters and file locations.

Using Speedstack Discussion of the Speedstack user interface; creating

and editing stackups.

Using Virtual Material mode; using Material Library

mode

Design rule checking Using the Speedstack Design Rule Checker to correct

stackup design errors.

Adding controlled impedance

structures

Working with the Si8000m/Si9000e field solvers to add

controlled impedance structures to the stackup model. Using the goal seeking facilities of the field solver to

obtain the correct impedance for a structure.

Frequency dependent

calculations (Speedstack Si)

Working with frequency dependent calculations to produce graphs and tables of insertion loss v frequency

for each stack substrate.

Using causal modelling

Using surface roughness compensation

Si Projects Working with Si Projects in Speedstack with Si8000m

and Si9000e

CITS test files Creating CITS test files for controlled impedance

structures in the stack

Speedstack Flex Working with flex-rigid stackups – using the Speedstack

Flex navigator

Speedstack HDI Working with HDI builds – sequential lamination

The Speedstack materials

libraries

Using the Speedstack materials libraries, creating new

libraries, adding material to the library. Accessing the

online libraries

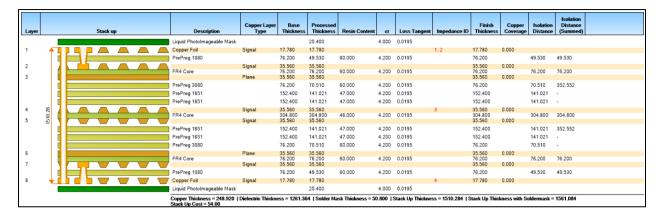

Printing stackup reports Printing Speedstack technical reports; using the stack

data tables, drill data tables, controlled impedance data tables, bill of materials tables and frequency dependent

tables and loss graphs

# **Contents**

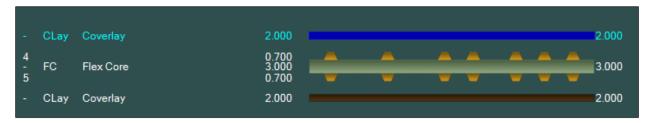

| Speedstack specifications                      | ii  |

|------------------------------------------------|-----|

| Personal computer requirements                 | iii |

| Introduction to Speedstack                     | 1   |

| Speedstack PCB Stackup Builder                 | 1   |

| Speedstack PCB                                 | 1   |

| Lossless calculations                          | 1   |

| Speedstack Si                                  | 1   |

| Frequency dependent calculations               | 2   |

| Causal modelling                               | 2   |

| Surface roughness modelling                    | 2   |

| Speedstack Flex                                | 2   |

| Speedstack HDI                                 | 3   |

| Rapid stackup creation                         | 3   |

| Easy stackup editing                           | 3   |

| High quality documentation and file format     | 4   |

| Integration with the Si8000m/Si9000e           | 4   |

| Materials library                              | 5   |

| Online / on-premise materials libraries        | 5   |

| Speedstack's Virtual Material mode             | 5   |

| Preferred builds                               | 5   |

| Dimensional information                        | 6   |

| High layer count boards                        | 6   |

| Supplier management                            | 6   |

| Graphical interface                            | 6   |

| Interfacing with other systems                 | 6   |

| Importing and exporting stackup information    | 6   |

| Converting imported electrical layers to cores | 7   |

| Structure net classes                          | 7   |

| Installing Speedstack                          | 8   |

| Installing and activating Speedstack           | 8   |

| Obtaining a Speedstack license                 | 8   |

| Uninstalling the software                      | 8   |

| Getting started with Speedstack                | 9  |

|------------------------------------------------|----|

| Online tutorial guides                         | 9  |

| Stackup Templates                              | 9  |

| Using Speedstack Stackup Builder               | 10 |

| Speedstack Stackup Builder                     | 10 |

| The Stack Editor                               | 10 |

| Controlled Impedance window                    | 11 |

| The Speedstack menu system                     | 12 |

| The File menu                                  | 12 |

| Opening projects                               | 12 |

| Saving stackups                                | 12 |

| Saving projects                                | 12 |

| Searching for stackups and project files       | 12 |

| Supplying search criteria                      | 13 |

| Importing Stackup information                  | 15 |

| IPC-2581 Rev B                                 | 15 |

| Setting import options                         | 16 |

| Setting display options                        | 16 |

| Sorting layer information                      | 16 |

| Assigning layer functions                      | 16 |

| Setting loss values                            | 17 |

| Ucamco Job Files                               | 18 |

| Integr8torJob files                            | 19 |

| XML files                                      | 20 |

| Zuken CR-8000                                  | 20 |

| Ucamco Integr8tor and Ucam format (.ssx)       | 20 |

| Converting imported electrical layers to cores | 20 |

| Exporting stackup information                  | 21 |

| Exporting to Coupon Generator (CGen)           | 21 |

| Export CITS File                               | 22 |

| Generating printed output                      | 22 |

| DXF, Gerber, CSV and XML files                 | 22 |

| Stackup images                                 | 22 |

| Cadence Allegro (IPC-2581 Rev B)               | 23 |

| Choosing export options                        | 23 |

| Mentor Graphics                                | 24 |

| Zuken CR-8000/DFM Centre                       | 24 |

| Ucamco Integr8tor and Ucam                     | 24 |

| Assigning properties to projects and stackups  | 24 |

| Backing up stackups and libraries              | 24 |

| Opening recent files                           | 24 |

| The Edit menu                                            | 25 |

|----------------------------------------------------------|----|

| Material Library and Virtual Material modes              | 25 |

| The View menu                                            | 26 |

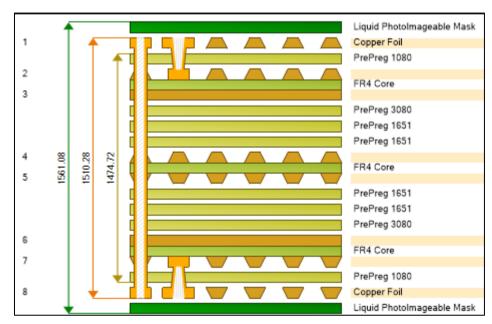

| Proportional Stack Viewer                                | 26 |

| The Tools menu                                           | 27 |

| The Units menu                                           | 27 |

| External Utility                                         | 27 |

| The Help menu                                            | 27 |

| Configuring Speedstack                                   | 28 |

| Environment and default settings                         | 28 |

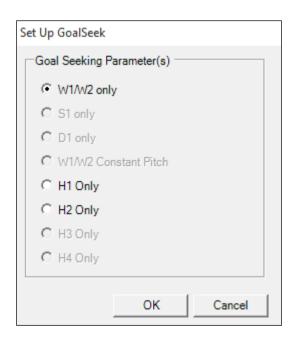

| General Options                                          | 28 |

| Structure Defaults                                       | 29 |

| Licensing                                                | 29 |

| Choosing default file locations                          | 30 |

| Specifying goal seeking parameters                       | 30 |

| Setting user defaults                                    | 31 |

| Specifying default CITS test file parameters             | 31 |

| CITS test methods                                        | 31 |

| Choosing background and stackup layer colours            | 32 |

| Miscellaneous Options                                    | 32 |

| Hatch Defaults                                           | 32 |

| Rebuild and Calculate Structures                         | 33 |

| Manufacturing Constraints                                | 33 |

| Editing and adding constraints                           | 34 |

| Set Target Stackup Thickness/Enable Finishing            | 35 |

| Finishing Options                                        | 36 |

| Simple Percentage Method                                 | 36 |

| Copper Coverage method                                   | 37 |

| Virtual Material mode                                    | 38 |

| Working with external utilities                          | 38 |

| The Speedstack toolbar                                   | 39 |

| File operations                                          | 39 |

| Stack building operations                                | 39 |

| Editing the stackup                                      | 40 |

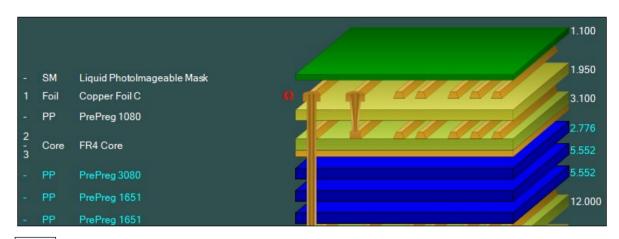

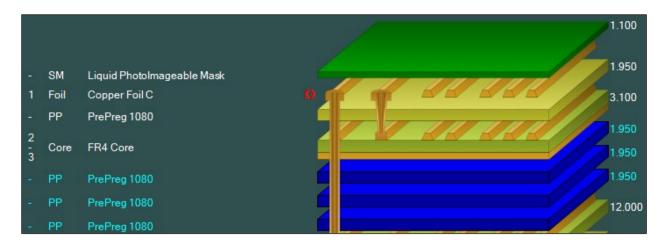

| Copying and pasting materials                            | 40 |

| Changing plane types                                     | 40 |

| Applying finishing                                       | 41 |

| Changing the stackup view                                | 41 |

| Managing the materials library                           | 41 |

| Exchanging data with the Si8000m or Si9000e Field solver | 42 |

| Creating and editing stackups (Virtual Material mode) | 43 |

|-------------------------------------------------------|----|

| Material Library and Virtual Material modes           | 43 |

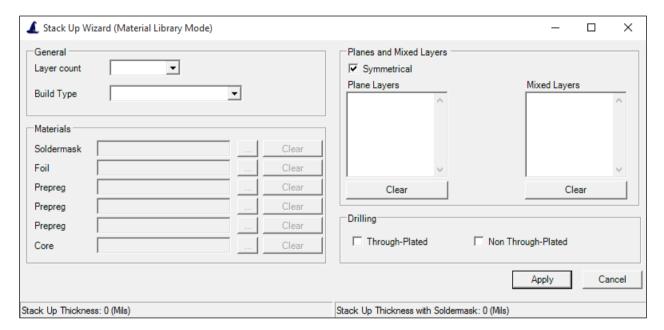

| Using the Stackup Wizard                              | 44 |

| Setting basic stack data                              | 45 |

| Adding drills                                         | 45 |

| Adding microvias                                      | 45 |

| Editing the stack                                     | 48 |

| Changing material properties                          | 48 |

| Choosing Symmetrical mode                             | 48 |

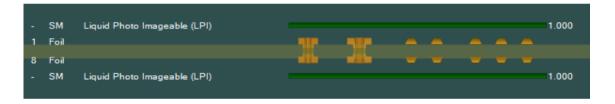

| Changing the material description                     | 48 |

| Changing electrical layers                            | 49 |

| Setting hatched planes                                | 49 |

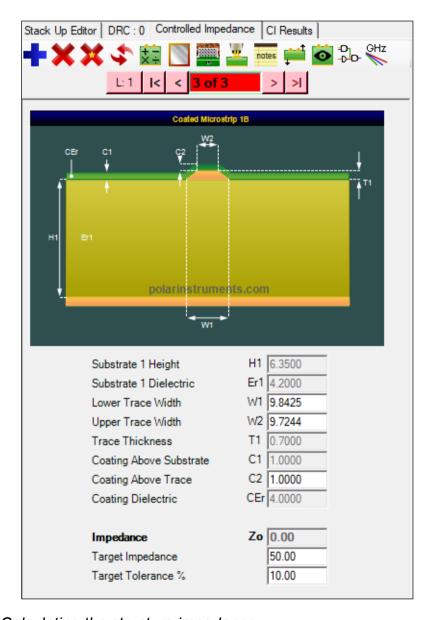

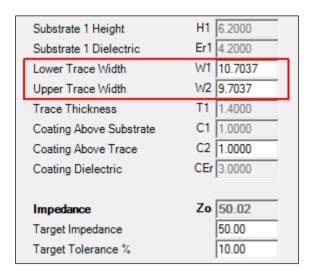

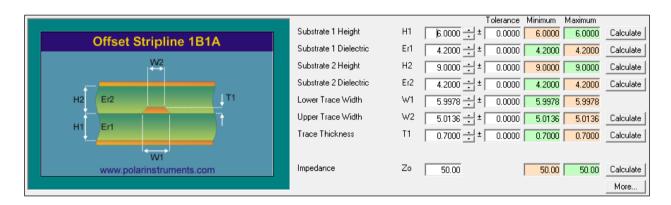

| Adding controlled impedance structures                | 50 |

| Calculating the structure impedance                   | 51 |

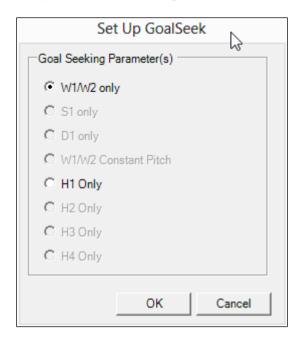

| Goal Seeking the target impedance                     | 52 |

| Mirroring structures                                  | 52 |

| Rebuilding the stack                                  | 53 |

| Creating and editing stackups (Material Library mode) | 54 |

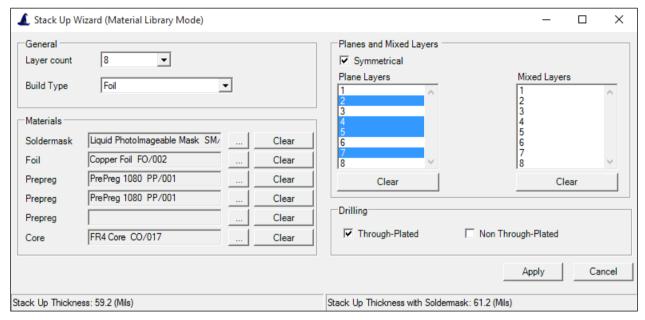

| Using the Stackup Wizard                              | 54 |

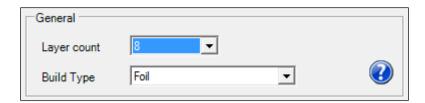

| Electrical layer count                                | 54 |

| Build type                                            | 54 |

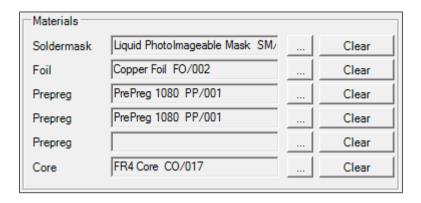

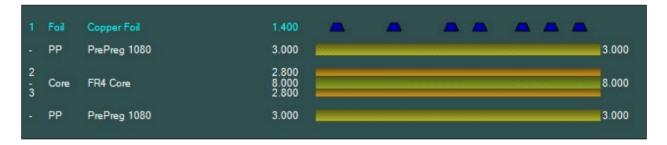

| Choosing stackup materials                            | 55 |

| Adding layers                                         | 55 |

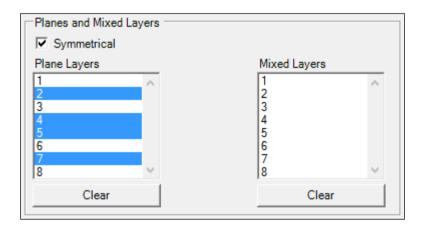

| Nominating power planes and mixed layers              | 56 |

| Adding drill information                              | 56 |

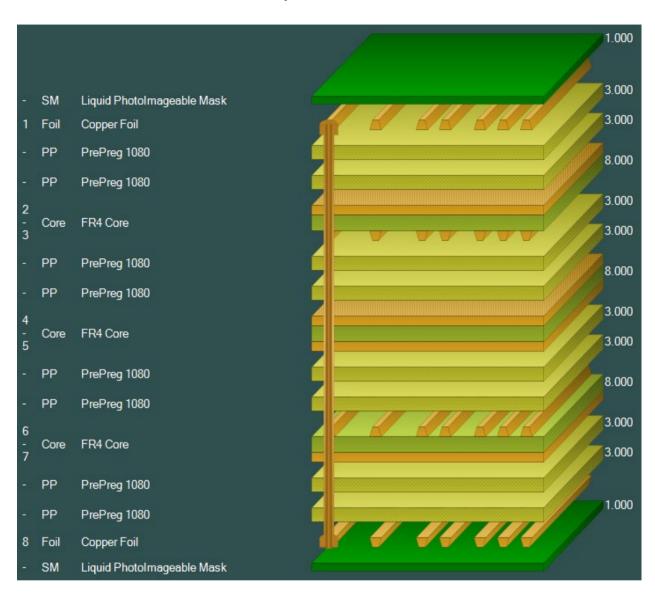

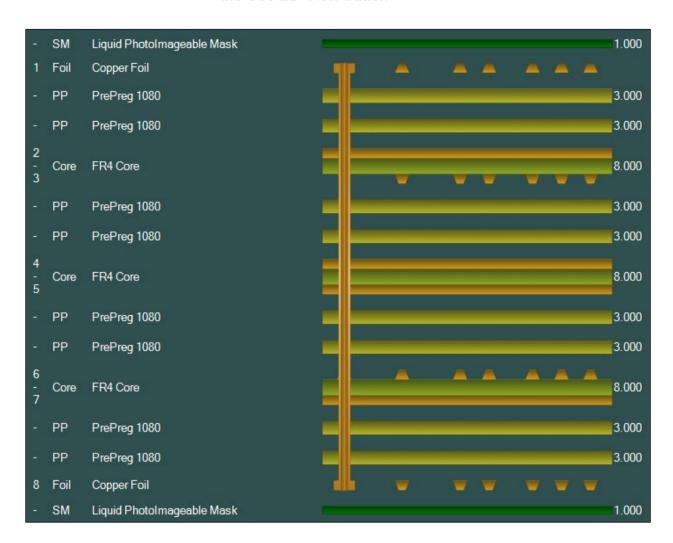

| Changing the stackup view                             | 58 |

| Filtering Materials                                   | 58 |

| Saving stackups                                       | 58 |

| Creating stackups manually                            | 59 |

| Editing the stack                                     | 59 |

| Adding layers to the stackup                          | 59 |

| Consistency of units                                  | 60 |

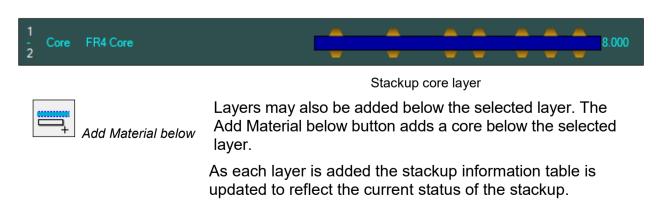

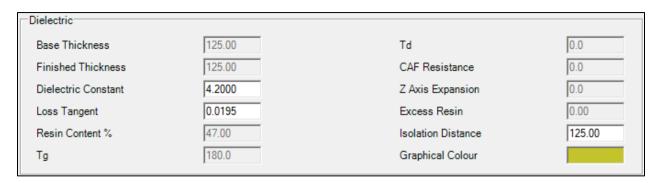

| Adding a core layer                                   | 60 |

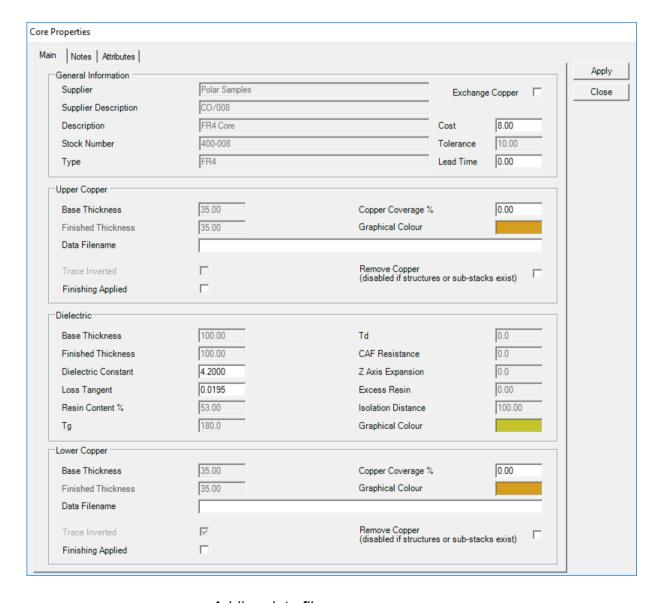

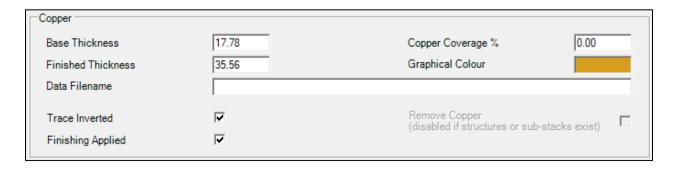

| Editing the selected layer properties                 | 62 |

| Adding data file names                                | 62 |

| Changing a layer function                             | 63 |

| Exchanging layers                                     | 63 |

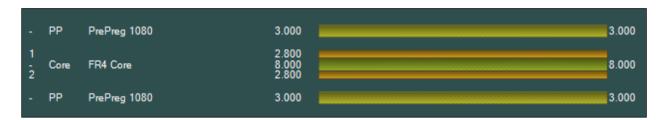

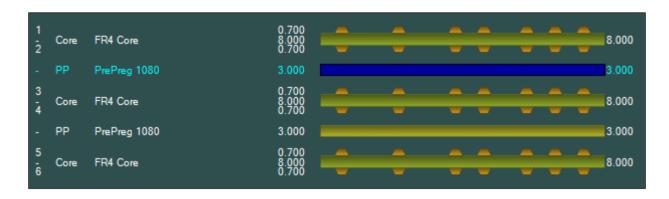

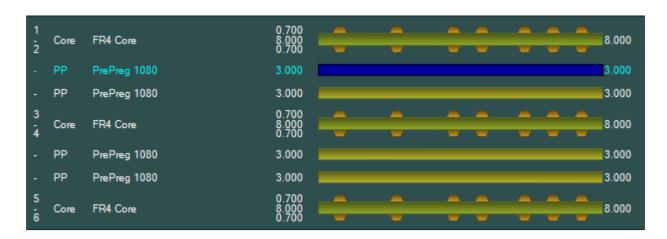

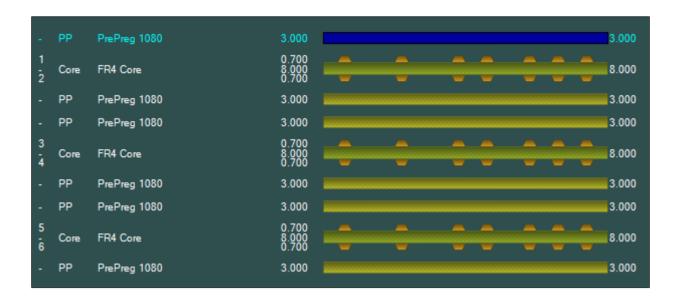

| Adding prepreg layers                                 | 63 |

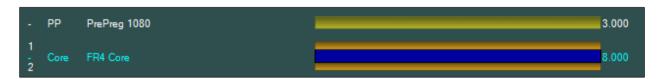

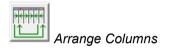

| Choosing the Display Data fields                      | 64 |

| Adding a foil layer                                   | 65 |

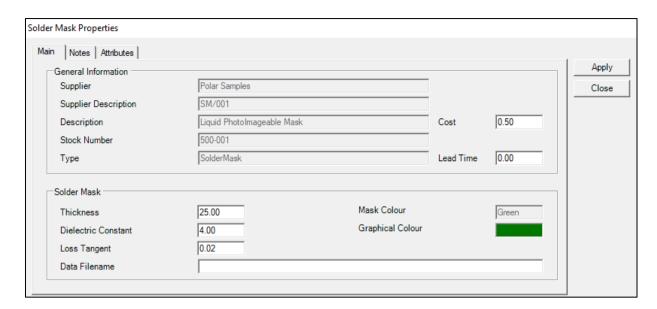

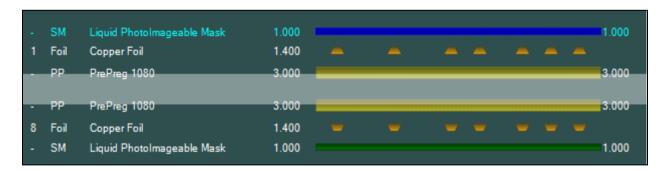

| Adding solder mask layers                             | 66 |

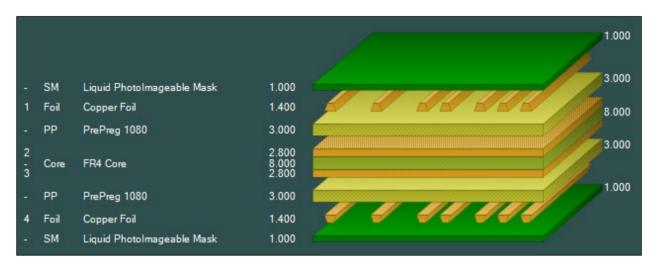

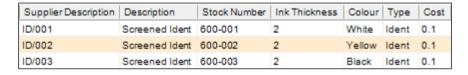

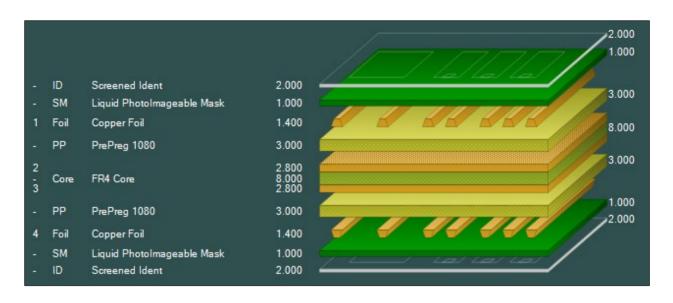

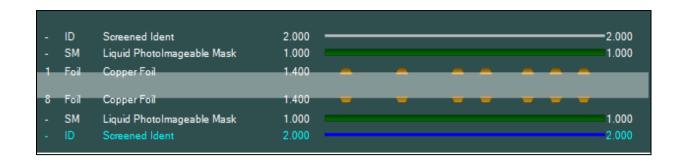

| Adding the Ident layers                                      | 66  |

|--------------------------------------------------------------|-----|

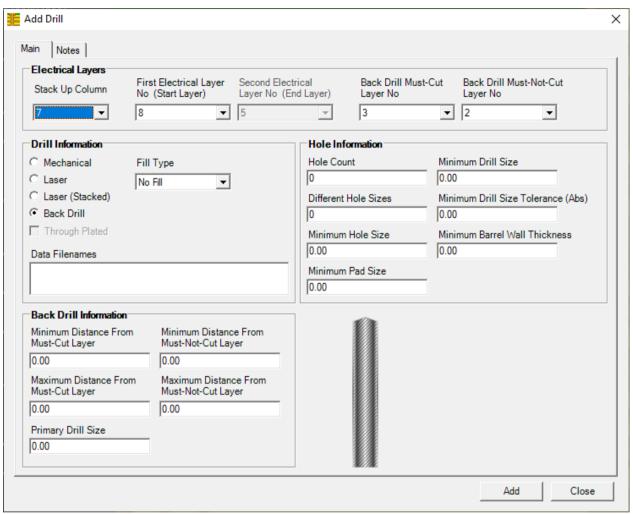

| Adding a drill                                               | 67  |

| Deleting drills                                              | 68  |

| Adding stack vias                                            | 68  |

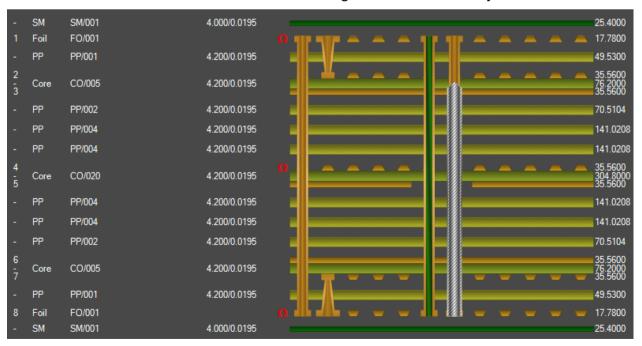

| Via stub removal (controlled depth drilling / back drilling) | 70  |

| Specifying back drills                                       | 71  |

| Specifying back drill information                            | 71  |

| Adding notes                                                 | 72  |

| Deleting a layer                                             | 72  |

| Copying a layer                                              | 72  |

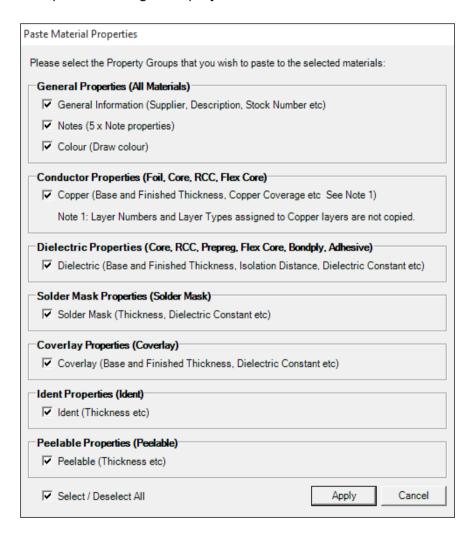

| Copying material properties                                  | 72  |

| Moving materials                                             | 74  |

| Applying finishing                                           | 74  |

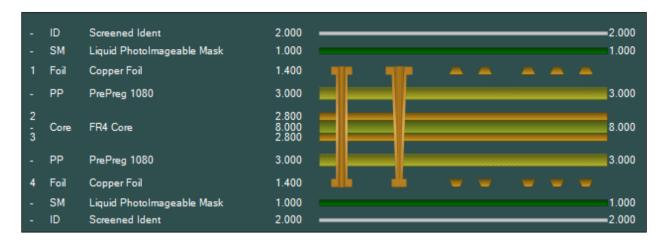

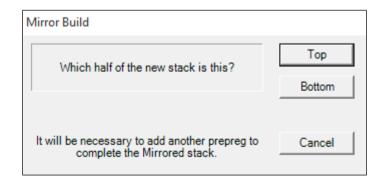

| Mirror Builds                                                | 75  |

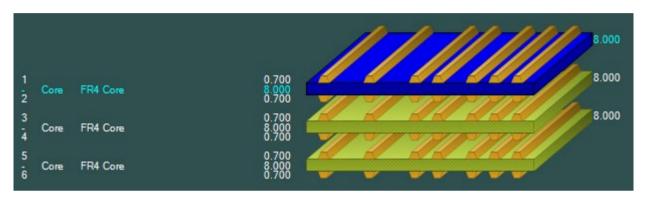

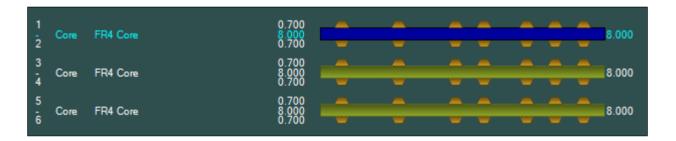

| Symmetrical Builds                                           | 76  |

| Creating a new stack                                         | 76  |

| Adding a prepreg layer in Symmetrical Mode                   | 76  |

| Adding a second prepreg layer                                | 77  |

| Adding foil, LPI Mask and Ident layers                       | 78  |

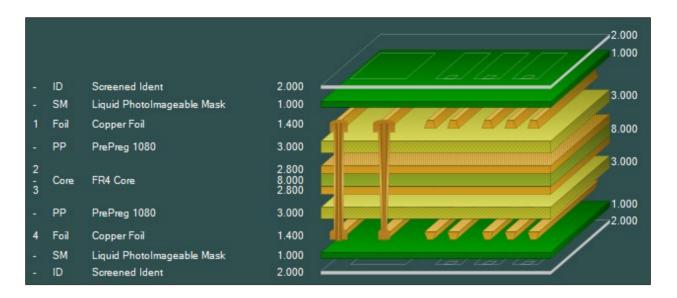

| Assigning ground planes                                      | 79  |

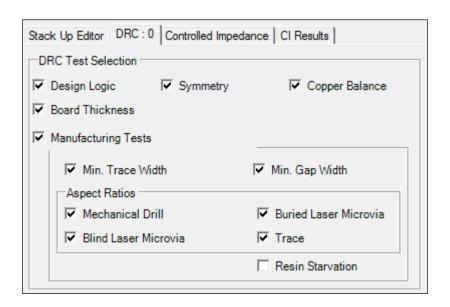

| Design rule checking                                         | 80  |

| Viewing design rule errors                                   | 80  |

| Correcting design rule errors                                | 82  |

| Creating and using manufacturing constraints                 | 82  |

| Editing constraints                                          | 83  |

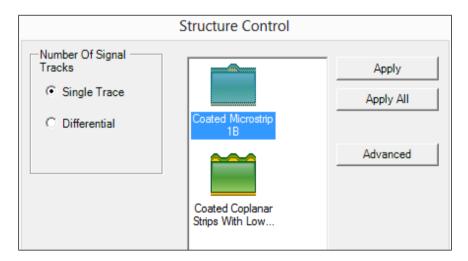

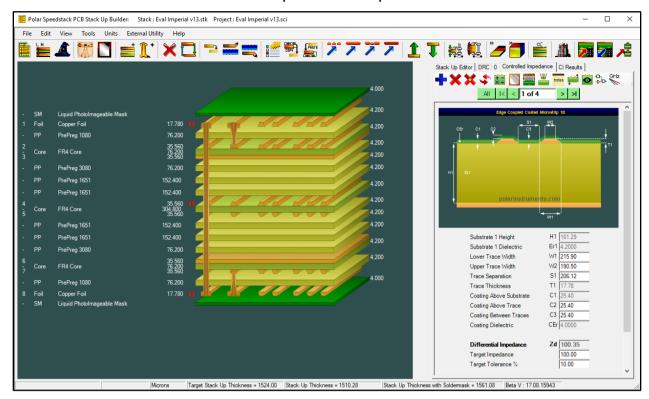

| Adding controlled impedance structures                       | 84  |

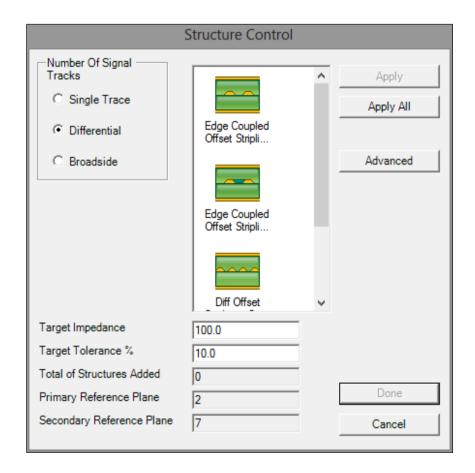

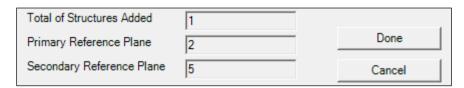

| Adding a controlled impedance structure                      | 84  |

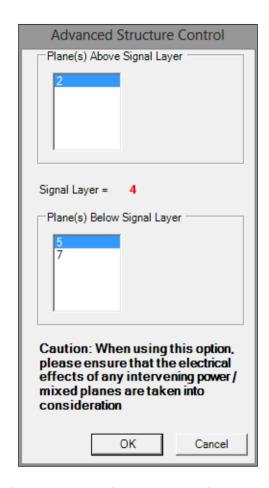

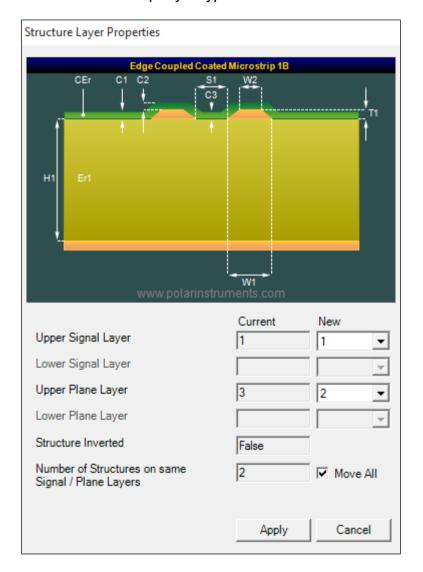

| Choosing reference planes                                    | 86  |

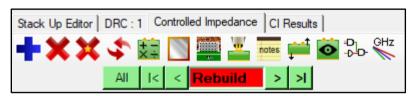

| Controlled impedance toolbar                                 | 88  |

| Changing parameter values                                    | 89  |

| Goal seeking with Speedstack                                 | 89  |

| Goal seeking with the Si8000m/9000e                          | 90  |

| Changing layer functionality                                 | 91  |

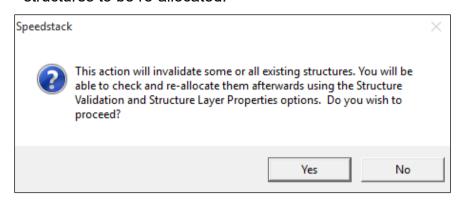

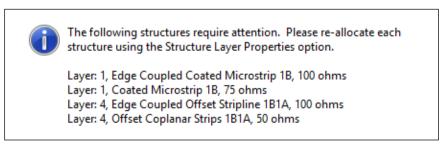

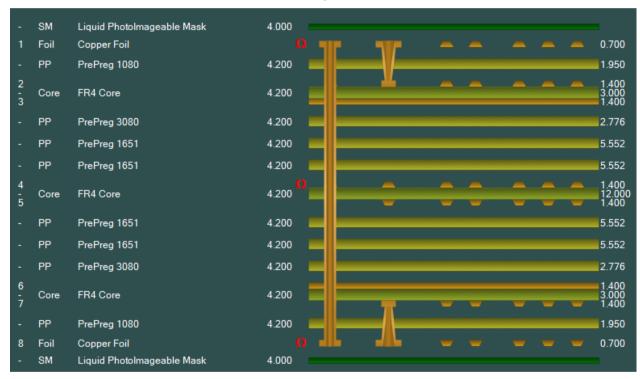

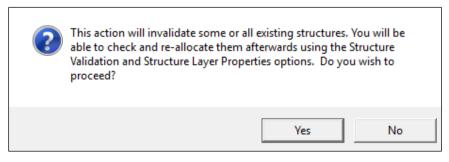

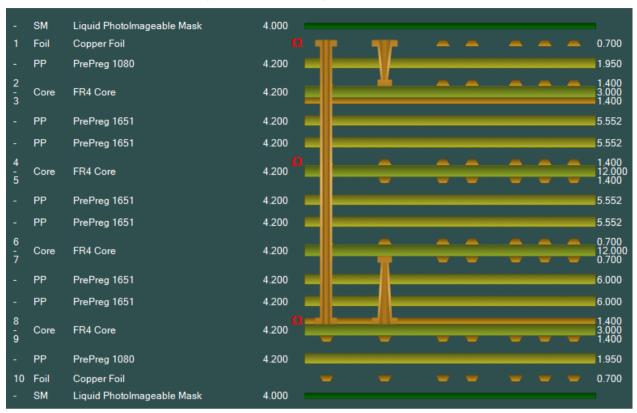

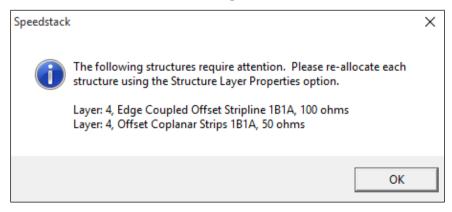

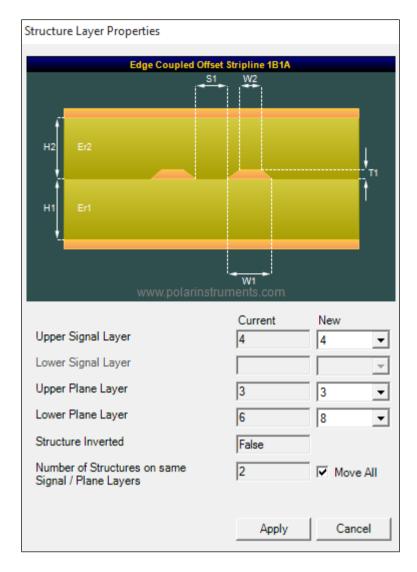

| Switching layer types and reallocating structures            | 92  |

| Increasing the layer count                                   | 95  |

| Structure net classes                                        | 97  |

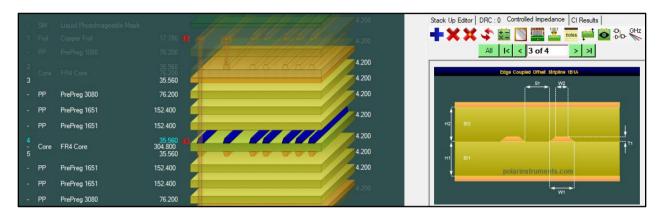

| Working with Si Projects in Speedstack and Si8000m/Si9000e   | 99  |

| Si Projects                                                  | 99  |

| Transferring structures from Speedstack to the field solver  | 99  |

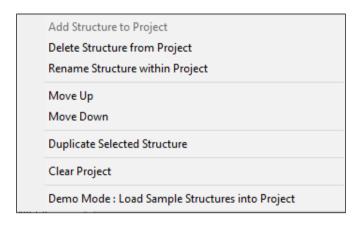

| Adding/deleting and modifying structures                     | 101 |

|                                                              |     |

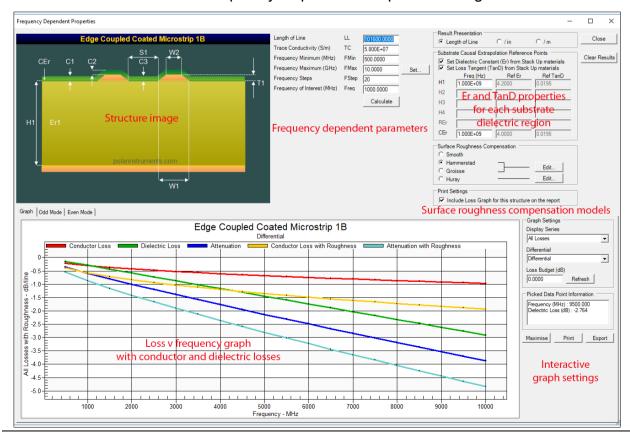

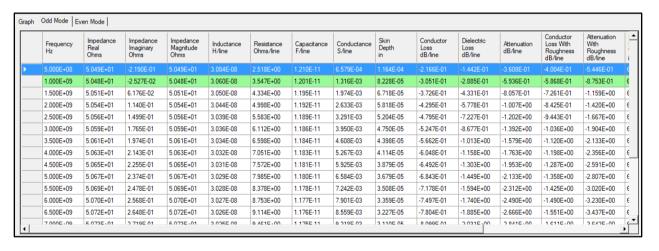

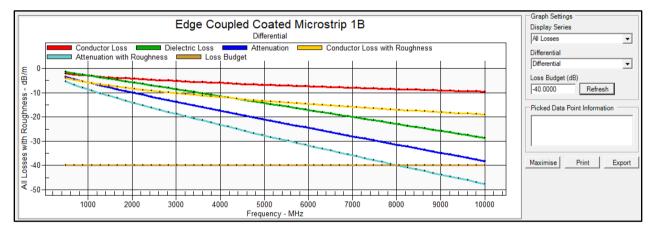

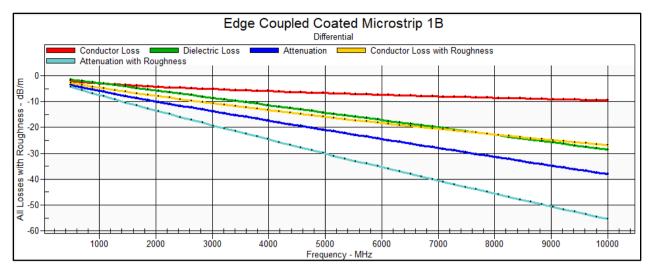

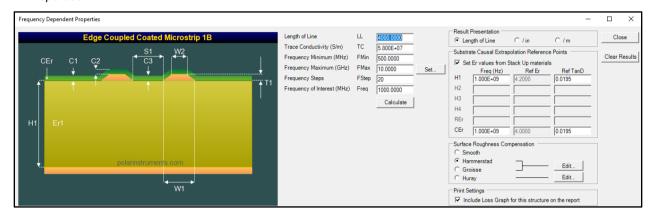

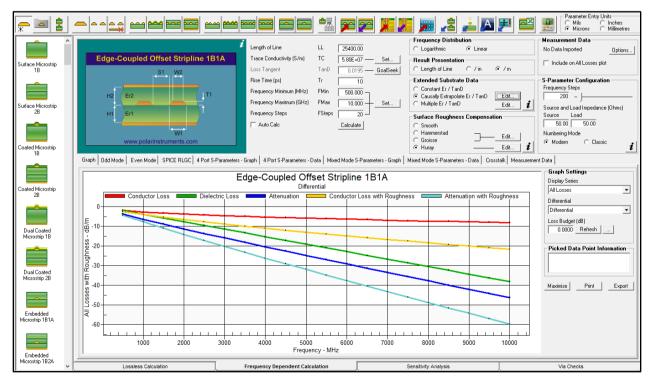

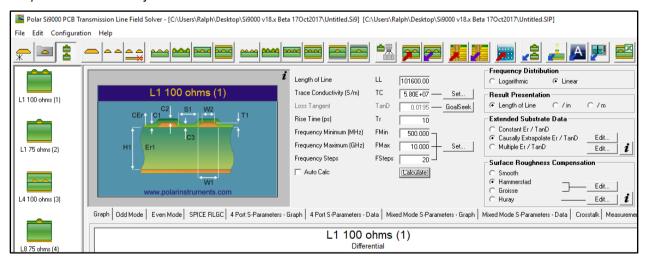

| Frequency dependent loss calculations (Speedstack Si only) | 102 |

|------------------------------------------------------------|-----|

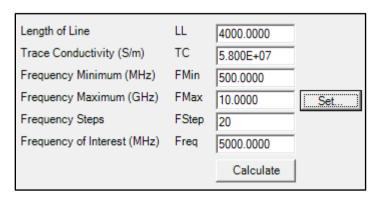

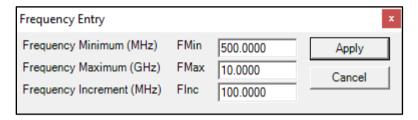

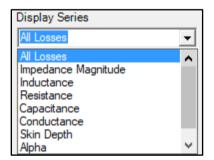

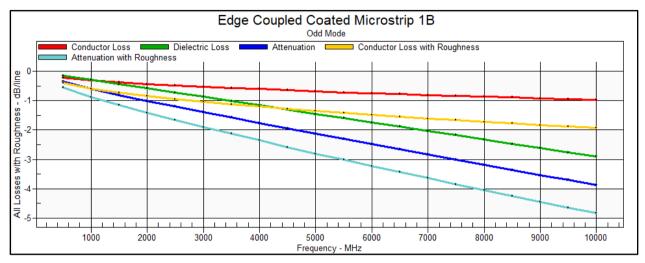

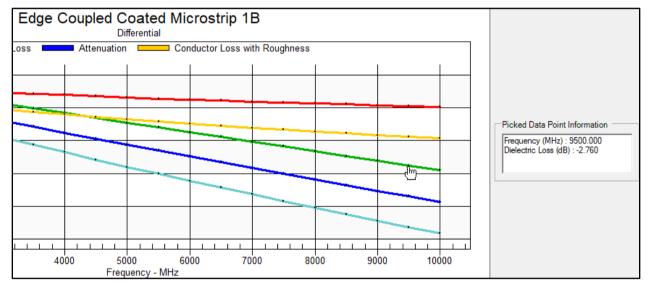

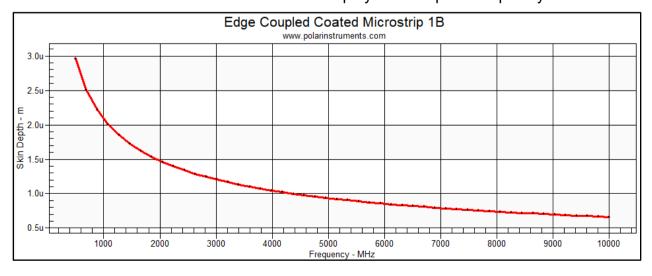

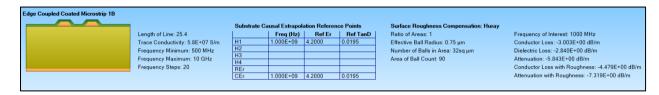

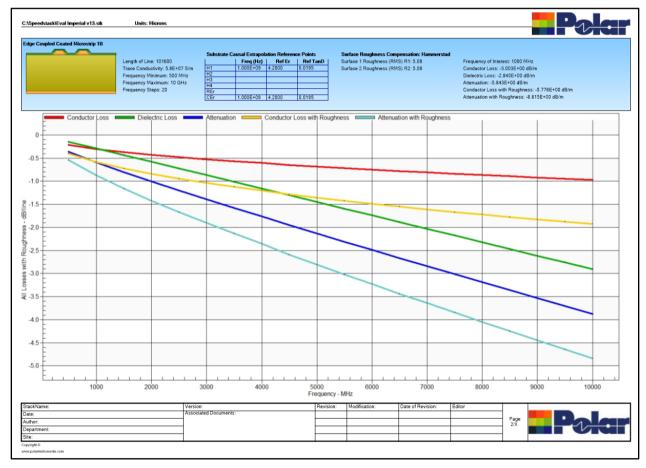

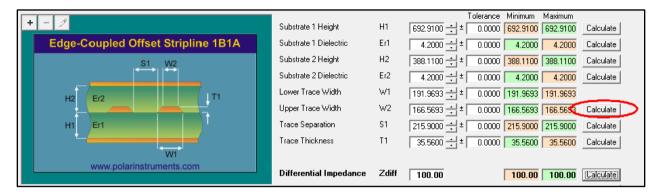

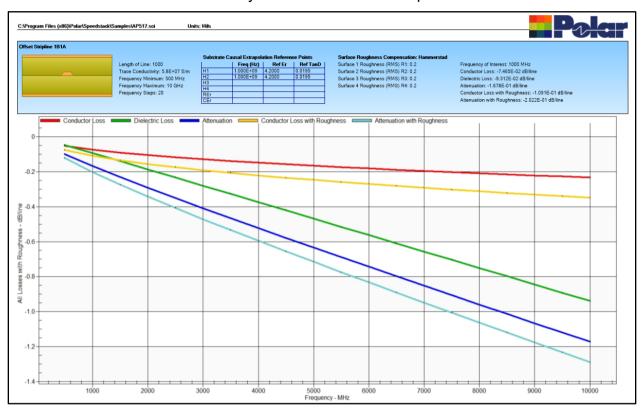

| Frequency dependent parameters                             | 103 |

| Presentation of results                                    | 104 |

| Graph settings                                             | 104 |

| Displaying the loss budget                                 | 106 |

| Material and surface roughness properties                  | 106 |

| Dielectric loss                                            | 106 |

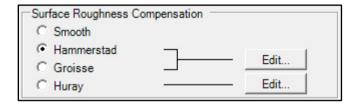

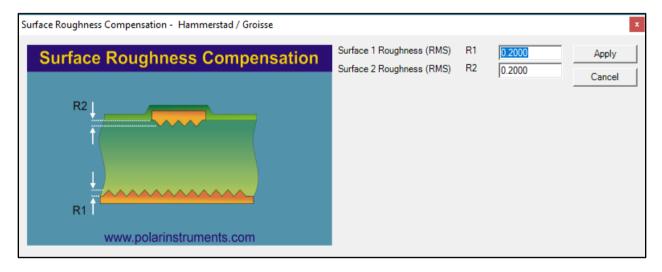

| Conductor losses – surface roughness compensation          | 107 |

| Surface roughness compensation methods                     | 108 |

| Hammerstad/Groisse methods                                 | 108 |

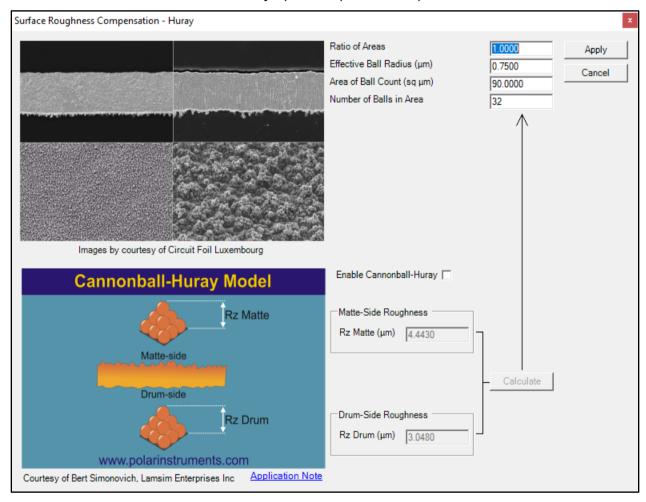

| Huray method                                               | 109 |

| Printing the technical report                              | 111 |

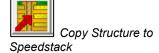

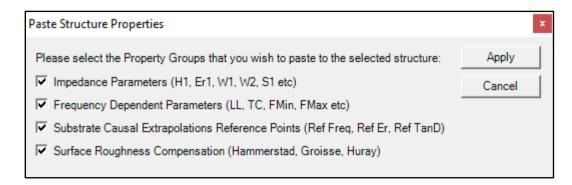

| Speedstack Si to Si9000e data transfer                     | 112 |

| Sharing structure properties                               | 112 |

| Transferring structures between Speedstack and Si9000e     | 115 |

| Transferring a single structure                            | 115 |

| Solving for impedance                                      | 116 |

| Running frequency dependent calculations                   | 116 |

| Transferring multiple structures via Si Projects           | 117 |

| Modifying structures                                       | 119 |

| Creating CITS test files                                   | 120 |

| Exporting the CITS test file                               | 120 |

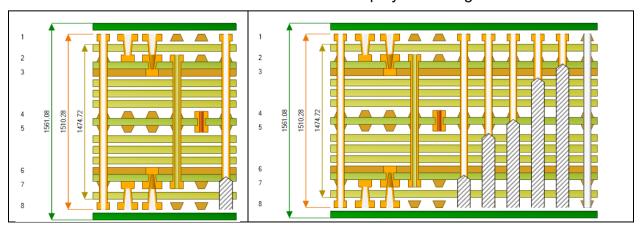

| Working with flex-rigid stackups                           | 121 |

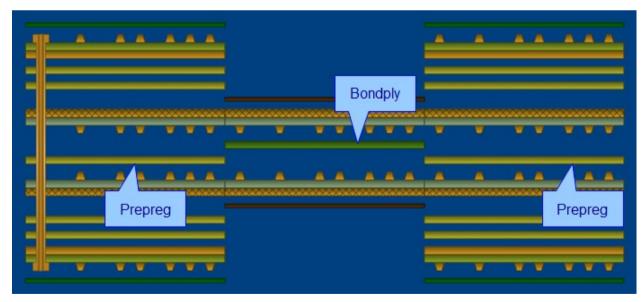

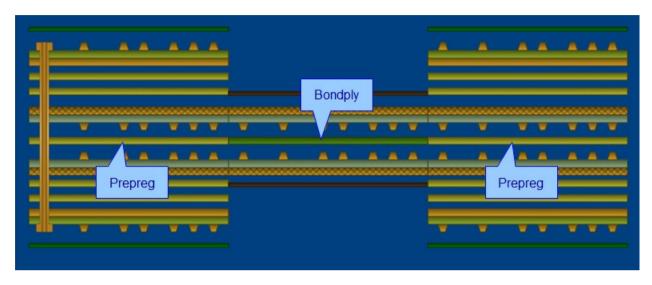

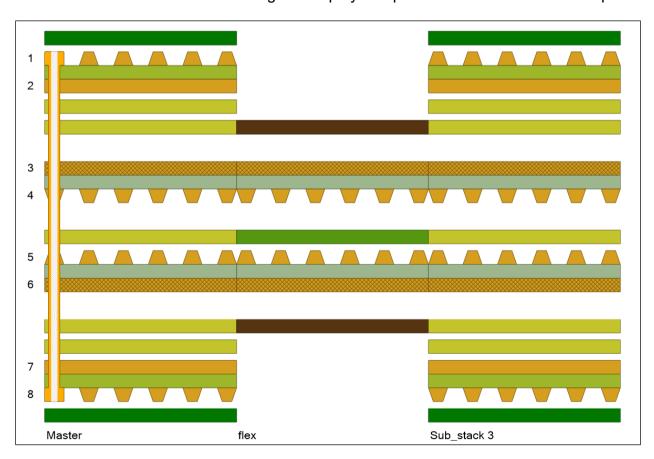

| Speedstack Flex                                            | 121 |

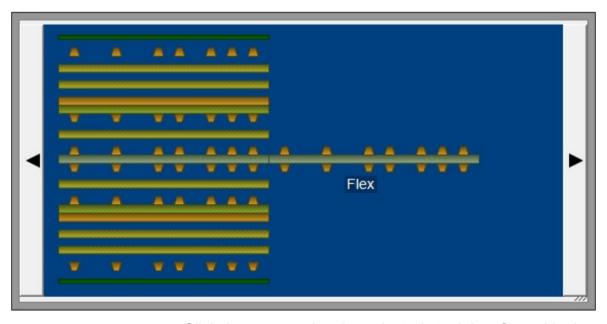

| The graphical stackup display                              | 121 |

| Mesh / Crosshatch ground planes                            | 122 |

| Internal Coverlays                                         | 122 |

| Definable colours per material                             | 122 |

| Enabling Speedstack Flex/HDI                               | 122 |

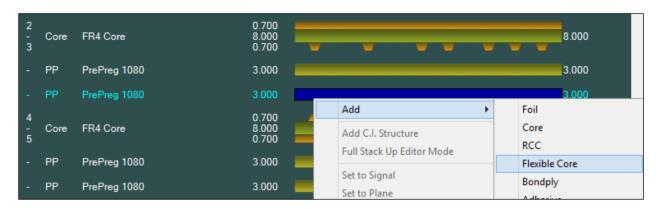

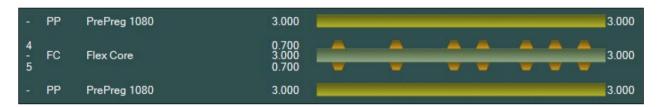

| Adding a flexible core                                     | 122 |

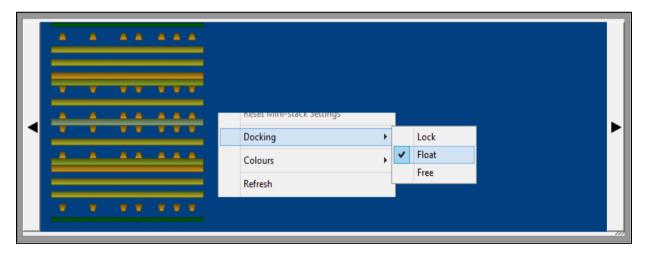

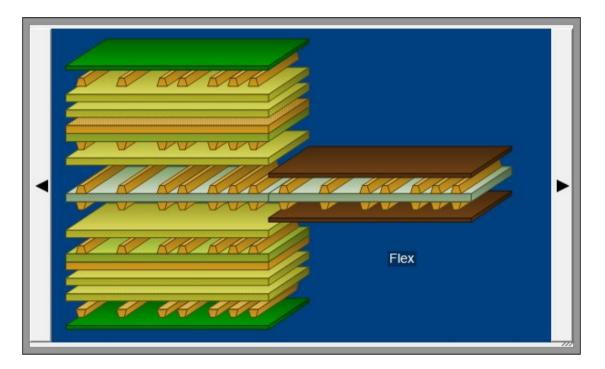

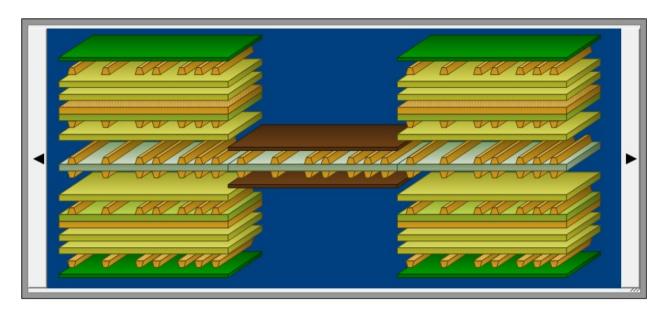

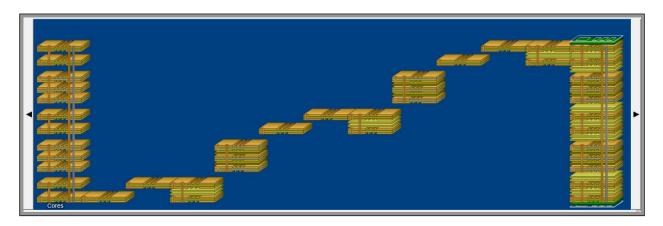

| Using the Navigator                                        | 123 |

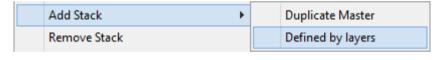

| Adding stacks                                              | 124 |

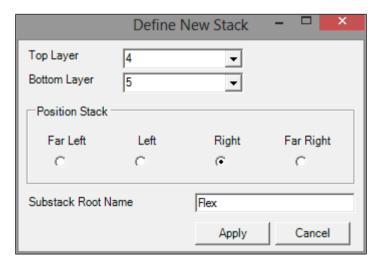

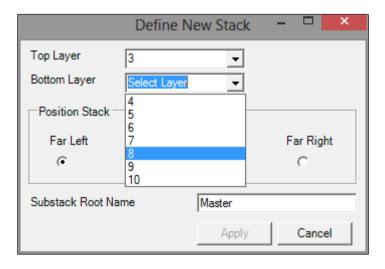

| Adding a new stack                                         | 125 |

| Defining new stacks                                        | 126 |

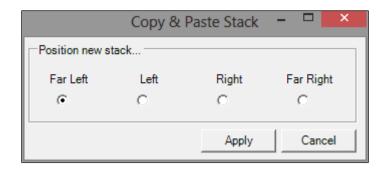

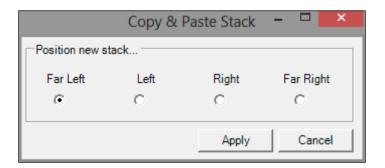

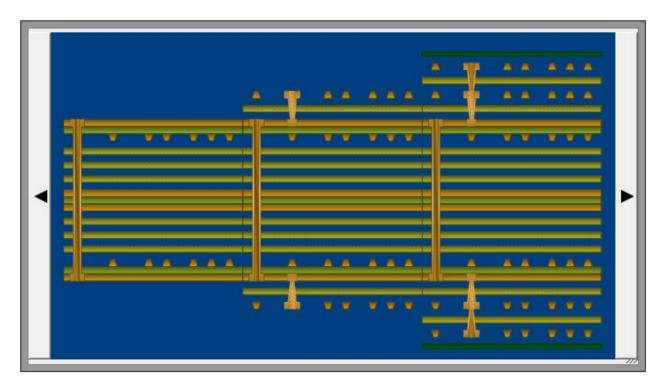

| Copying and pasting stacks                                 | 126 |

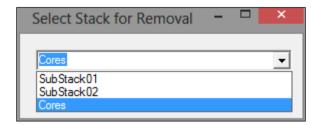

| Removing stacks                                            | 127 |

| Aligning materials in the navigator                        | 127 |

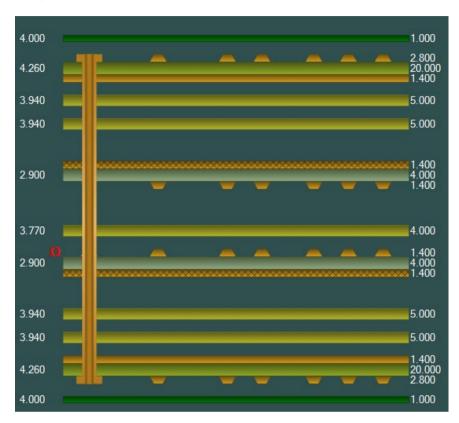

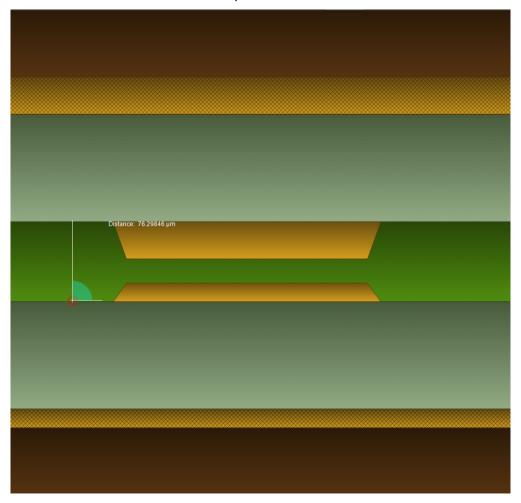

| Displaying the stack in Proportional View                  | 129 |

| Using the Ruler within Proportional view                   | 130 |

| Working with HDI builds                                | 131 |

|--------------------------------------------------------|-----|

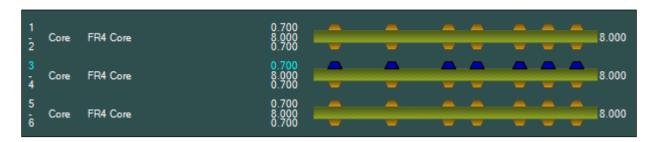

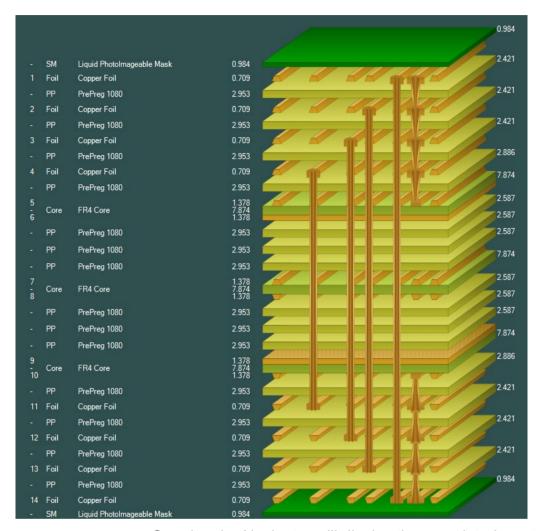

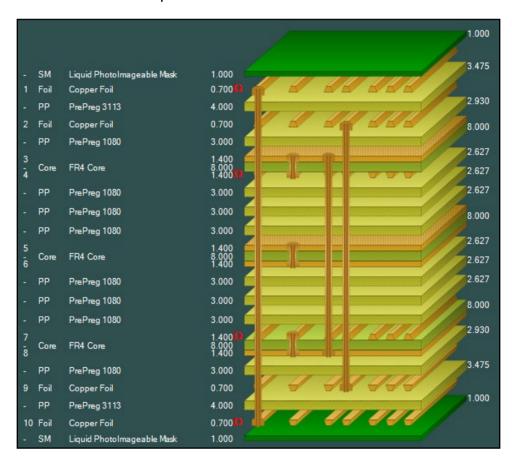

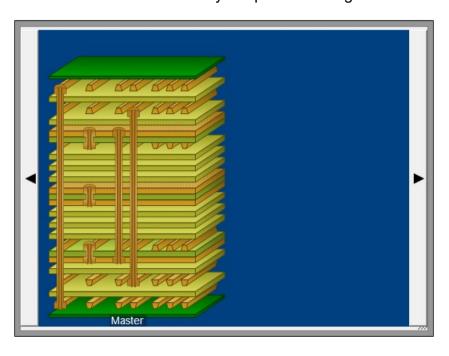

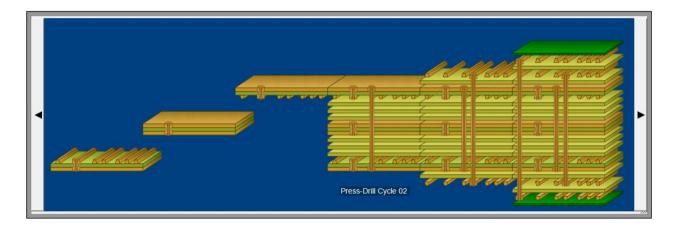

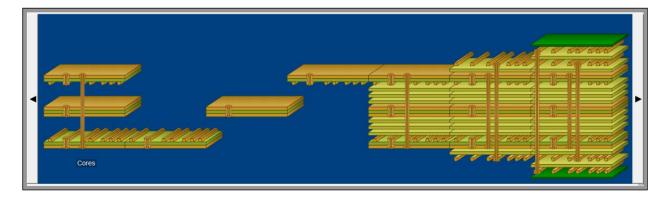

| Speedstack HDI                                         | 131 |

| Easy graphical stackup display                         | 131 |

| Sub-stack reordering                                   | 131 |

| HDI builds                                             | 131 |

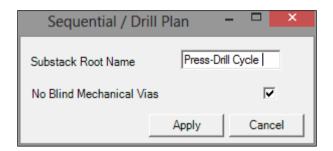

| Sequential plan                                        | 131 |

| Drill plan                                             | 131 |

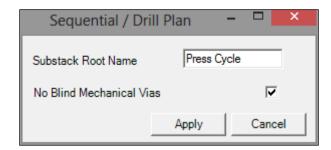

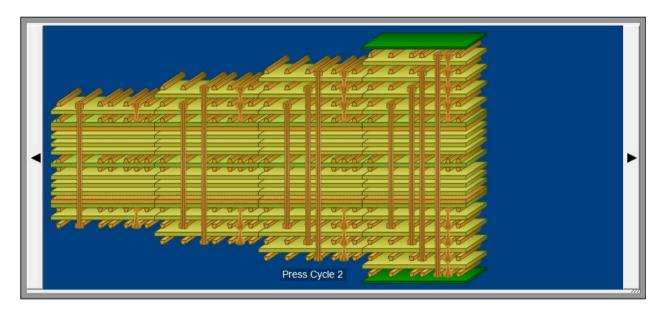

| Using the Sequential Plan                              | 137 |

| Using the Drill Plan                                   | 139 |

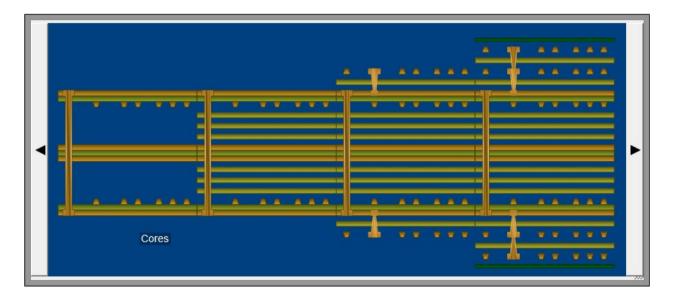

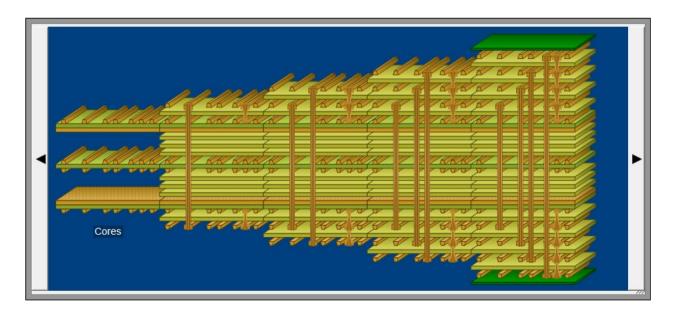

| Exposing cores                                         | 140 |

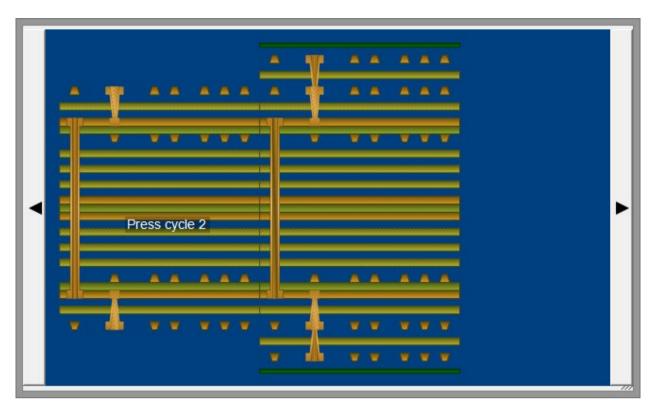

| Working with multiple press cycles                     | 141 |

| Printing the Navigator screen                          | 142 |

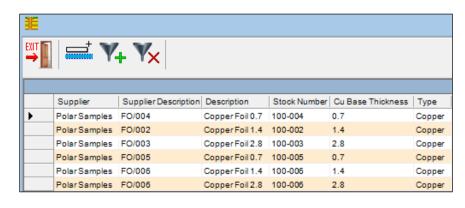

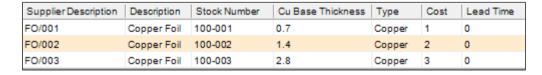

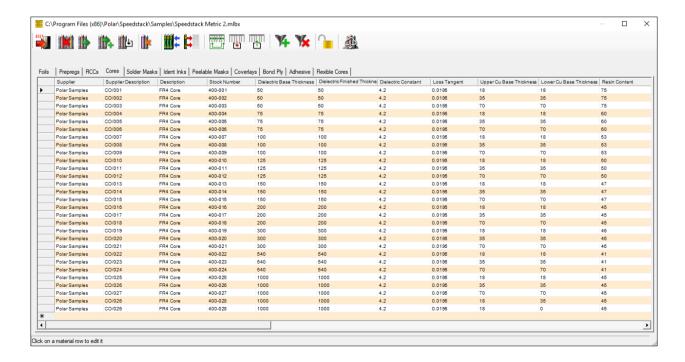

| Using Speedstack materials libraries                   | 143 |

| Working with the materials libraries                   | 143 |

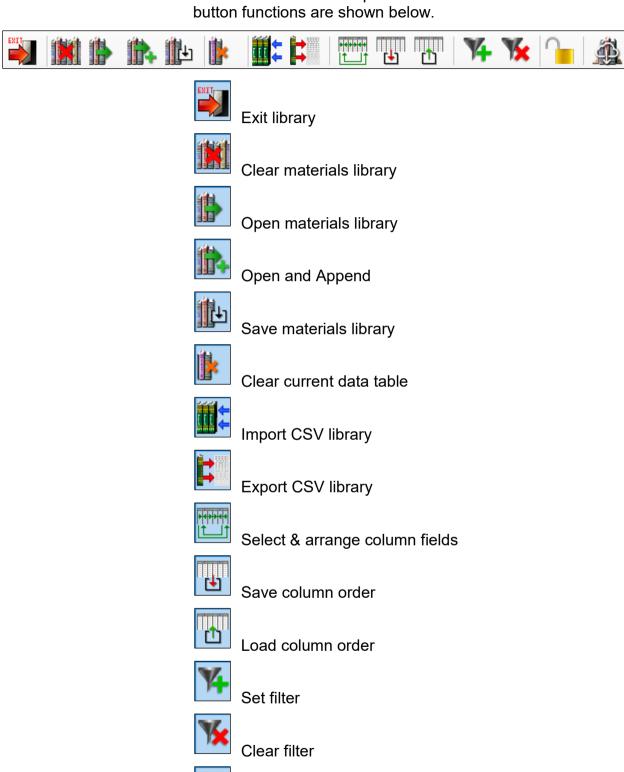

| Materials library toolbar                              | 144 |

| Opening a library                                      | 145 |

| Opening and appending a library                        | 145 |

| Creating a new library                                 | 145 |

| Importing material to the Speedstack materials library | 145 |

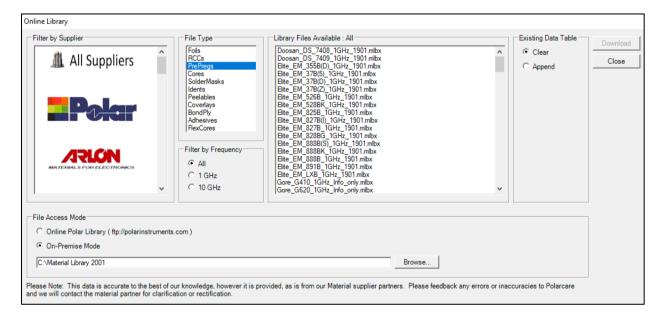

| Using the Online Library                               | 145 |

| Importing from the Polar Online Library                | 145 |

| Filtering libraries by frequency                       | 146 |

| On-Premise libraries                                   | 146 |

| Downloadable mlbx files                                | 147 |

| Choosing material files                                | 147 |

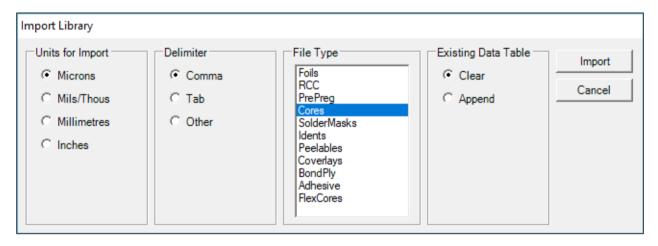

| Importing from local material files                    | 147 |

| Replacing existing material tables                     | 148 |

| Adding material data to an existing library            | 148 |

| Adding new material to the data tables                 | 149 |

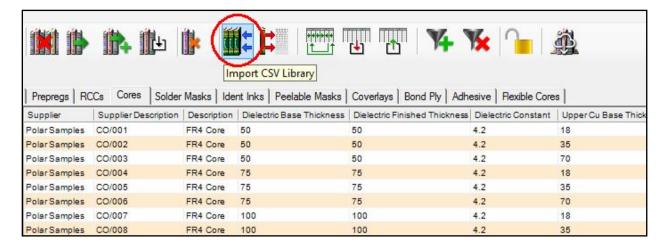

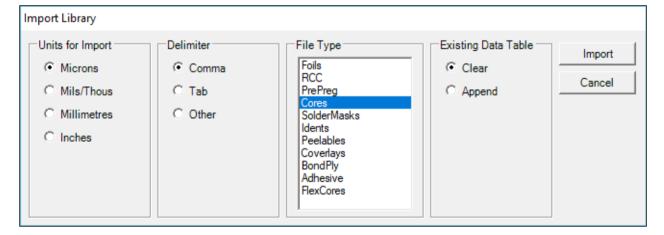

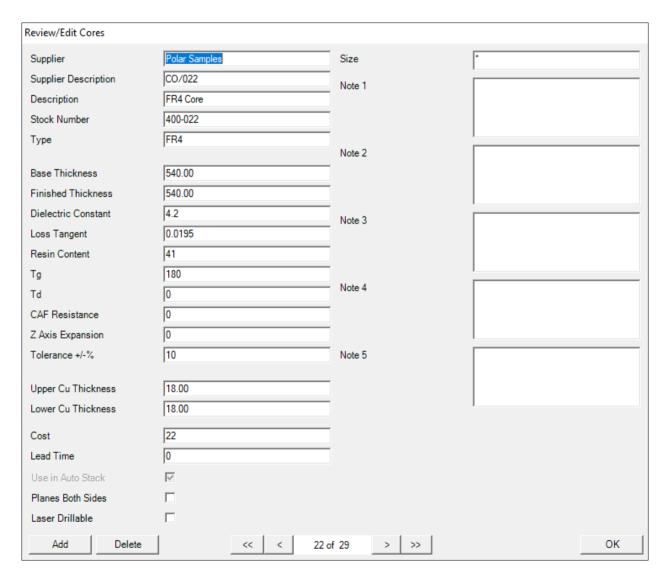

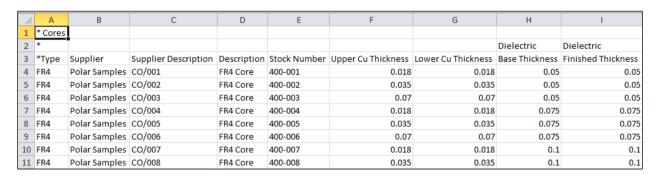

| Importing material to the data tables                  | 150 |

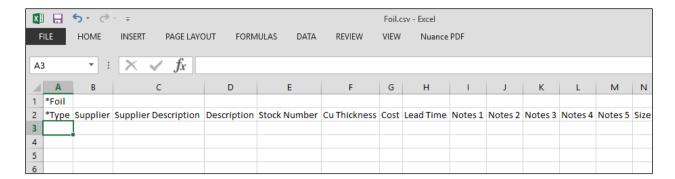

| Library sample files                                   | 150 |

| Creating a new materials library table                 | 150 |

| Adding material data to an existing library            | 152 |

| Selecting Materials from the Library                   | 152 |

| Column Order (Materials Library)                       | 152 |

| Arranging Columns in Library Forms                     | 152 |

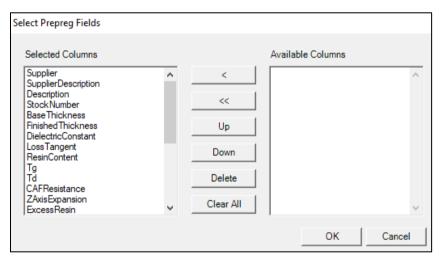

| Filtering Materials                                    | 153 |

| Building the filter string                             | 153 |

| Using the Like operator                                | 153 |

| Locking the library                                    | 154 |

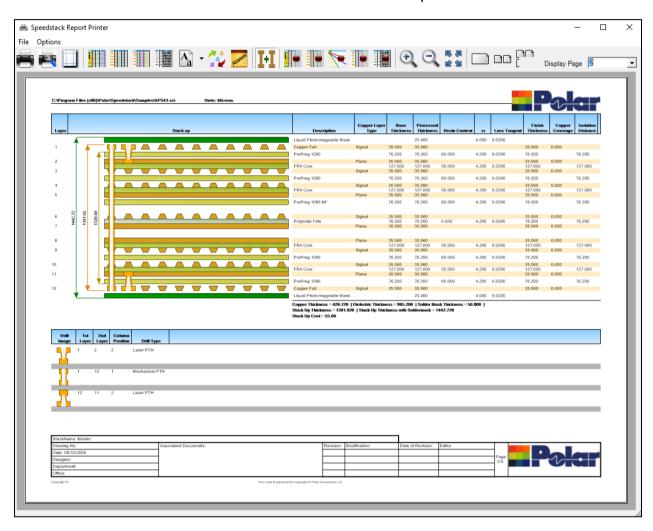

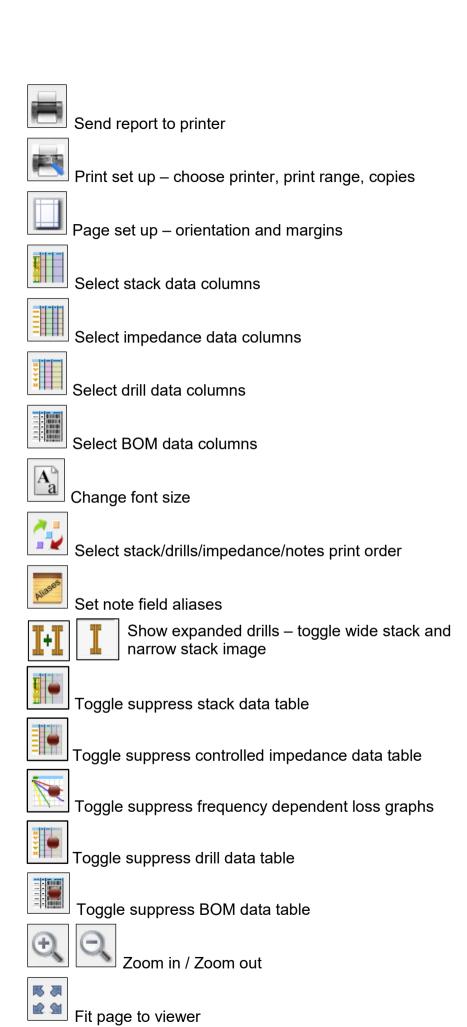

| Printing stackup information          | 155 |

|---------------------------------------|-----|

| Speedstack Report Printer toolbar     | 155 |

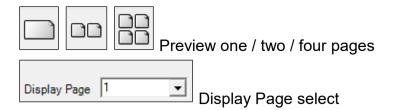

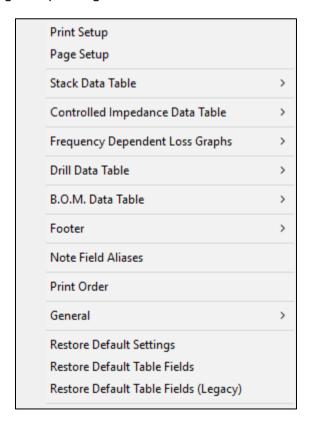

| Speedstack Report Printer menu system | 157 |

| File menu                             | 157 |

| Options menu                          | 157 |

| Print Setup                           | 157 |

| Page Setup                            | 158 |

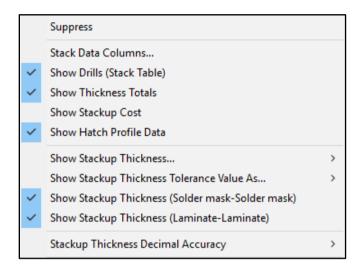

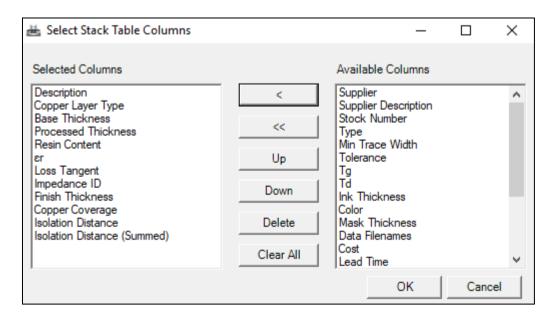

| Stack Data Table                      | 158 |

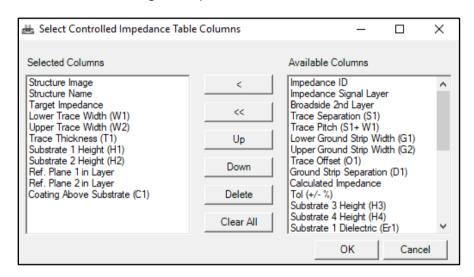

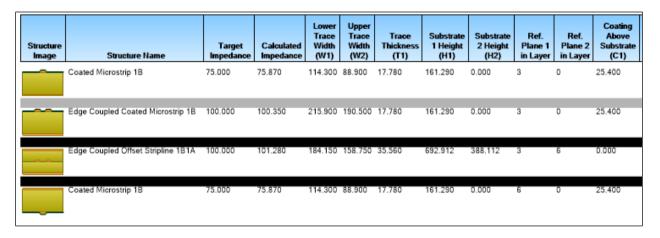

| Controlled Impedance Data Table       | 160 |

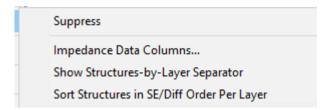

| Grouping structures by layer          | 160 |

| Sorting impedance structures by type  | 161 |

| Frequency dependent loss graphs       | 162 |

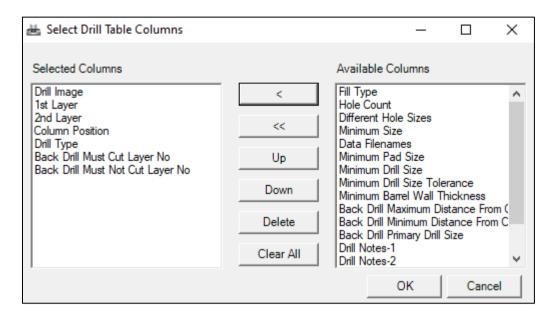

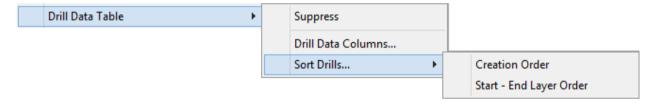

| Drill DataTable                       | 163 |

| Showing expanded drills               | 163 |

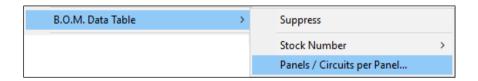

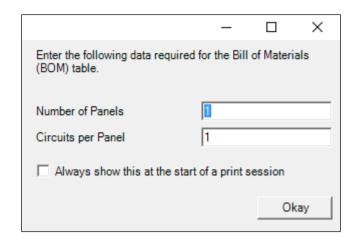

| Bill of Materials Table               | 164 |

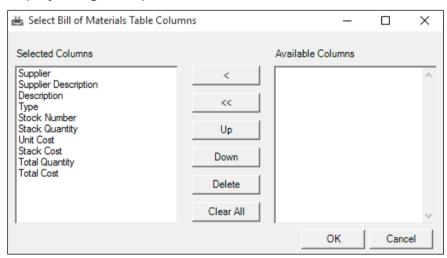

| Choosing the bar code font            | 166 |

| Choosing the start/stop character     | 166 |

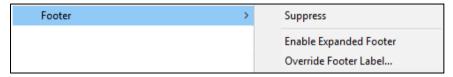

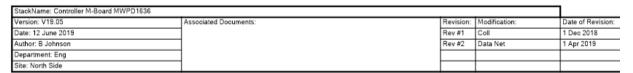

| Footer                                | 167 |

| Suppressing the footer                | 167 |

| Using the expanded footer             | 167 |

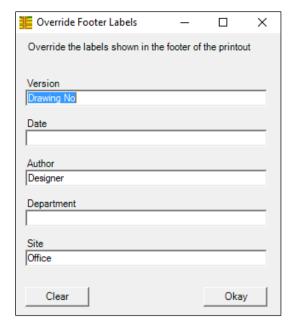

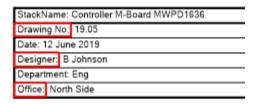

| Overriding the footer labels          | 167 |

| Note Field Aliases                    | 168 |

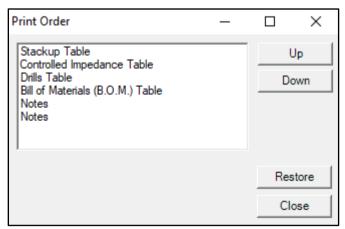

| Print Order                           | 168 |

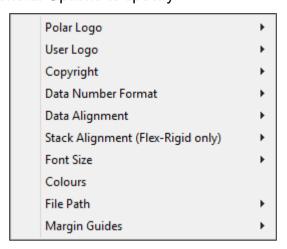

| General options                       | 169 |

# **Introduction to Speedstack**

# Speedstack PCB Stackup Builder

Polar Instruments Speedstack PCB Stackup Builder is designed to accelerate the PCB stack design process and deliver significant reductions in the amount of time consumed in PCB stackup documentation and control. Given designer specifications the PCB fabricator can use the Speedstack Stackup Builder to create in just a few steps the most cost effective stack for the range of available materials. Speedstack offers interconnect designers (PCB layout engineers), PCB front-end engineers and fabricators a fast and professional solution to layer stackup creation and documentation. Speedstack provides formal documentation for everyone involved in ensuring the correct materials are used in the build process.

# Speedstack PCB

Speedstack PCB is a versatile PCB layer stackup design tool featuring powerful and easy to use graphical stackup editing capabilities. For PCB fabricators Speedstack PCB interfaces with the industry standard Polar Si8000m PCB Multiple Dielectric Controlled Impedance Field Solver.

# Lossless calculations

It includes a link and license for the Si8000m, using the proven Si8000m to provide the impedance data for the stack. In addition, Speedstack PCB licence holders have full access to the stand alone Si8000m Quick Solver.

Speedstack PCB is especially tailored for PCB fabricators and PCB brokers – anyone with a requirement to design or communicate controlled impedance PCB stackups.

Speedstack PCB customers are able to share stackups and read impedance requirements from designers who are using Speedstack Si PCB Insertion Loss Field Solver.

# Speedstack Si

For electronic engineers involved in stackup design Speedstack Si interfaces with the Polar Si9000e PCB Insertion Loss Field Solver. Both Speedstack Si and Speedstack PCB are able to directly output controlled impedance test files associated with each stackup. For the fabricator this is an ideal way to link the impedance test requirements to a particular job. For the OEM this offers a

clear method of sending impedance test specifications out to suppliers or brokers. Designers and fabricators can work together and select the best material combinations for minimising build costs. Fabricators can share their in house material libraries with OEMs and ensure the most effective material choice is employed in the build.

#### Frequency dependent calculations

Speedstack Si caters for frequency dependent calculations and adds comprehensive insertion loss calculation capability into Speedstack; insertion loss can be graphed over a user-specifiable frequency range. Frequency dependent structure properties allow for insertion loss calculation: trace conductivity, frequency range and result presentation mode. Loss results can be shown in dB/m, dB/inch or dB/LL (length of line.)

#### Causal modelling

Frequency dependent parameters include length of line, trace conductivity, dielectric constant and loss tangent, frequencies of interest and causal extrapolation points for each substrate and also support amalgamated dielectric structures. Frequency dependent calculations employ causal interpolation of dielectric constant using Svensson-Djordjevic modelling. Library materials tables include dielectric constant and loss tangent fields and substrate causal extrapolation reference points values may be set either manually or automatically from the library (virtual material mode supports loss tangent in laminates and soldermask.)

#### Surface roughness modelling

Speedstack includes surface roughness compensation in frequency dependent calculations, supporting Hammerstad, Groisse and Cannonball-Huray surface roughness modeling methods.

Bidirectional copy and paste between Speedstack and the Si9000e transmission line field solver allows for quick transfer of structure parameters.

Technical reports optionally include insertion loss graphs for user-nominated structures.

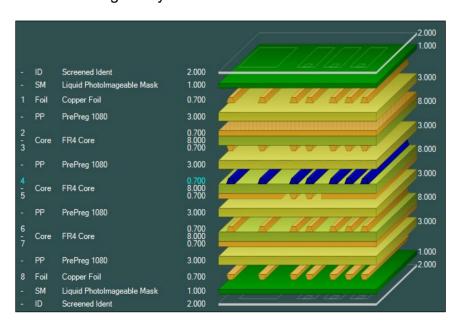

# Speedstack Flex

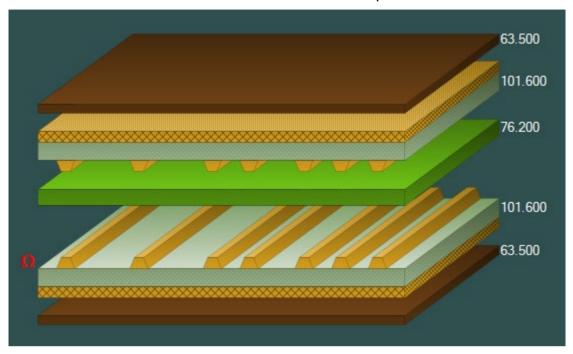

Speedstack Flex allows OEM designers to create accurate and efficient flex-rigid PCB stackups in just a few minutes, with error-free documentation for tighter control over the finished board. For PCB fabricators, Speedstack Flex provides the flexibility to quickly calculate the impact of substituting alternative materials to improve manufacturability and reduce cost while maintaining the specified parameters

and performance of the board. Speedstack Flex can be used in conjunction with the Si8000m and Si9000e field solvers when modelling and documenting mesh/crosshatch ground. Structure data and mesh geometry can be readily shared between Speedstack and the field solvers. The Navigator provides a clear contextual view of the rigid and flexible stacks within a flex-rigid build and allows easy alignment of displayed materials between stacks. The associated technical report also supports different materials on the same dielectric layer, improving the clarity of documentation between the stackup designer and fabricator.

# Speedstack HDI

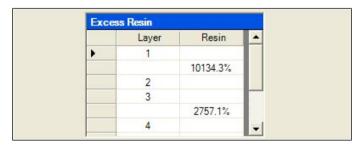

Speedstack's Navigator quickly guides you through the sequential sub-stack lamination sequence and presents the complete assembly in a parsed graphical display that shows each phase of the multi-step lamination sequence of an HDI PCB. There is no limit to the number of press cycles that can be documented.

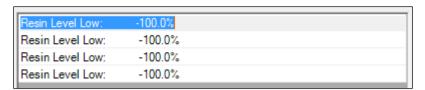

Resin check / excess resin algorithms determine the order in which the materials are pressed together and return useful resin percentage information that can be used to determine potential de-lamination problems.

User-definable settings within the navigator allow engineers to display layers in transparent, invisible or 3D mode. Speedstack HDI makes re-ordering and renaming sub-stacks quick and easy with the Navigator. This is especially useful for HDI constructions.

#### Rapid stackup creation

Users may specify the stackup semi-automatically with the powerful Stackup Wizard or alternatively build the stack manually, layer by layer. Speedstack is flexible and allows full manual editing of stacks created by the Stackup Wizard.

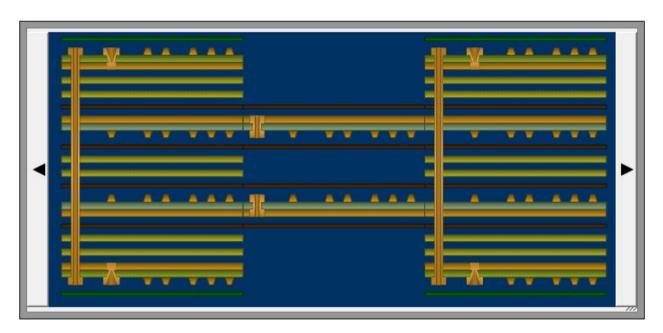

# Easy stackup editing

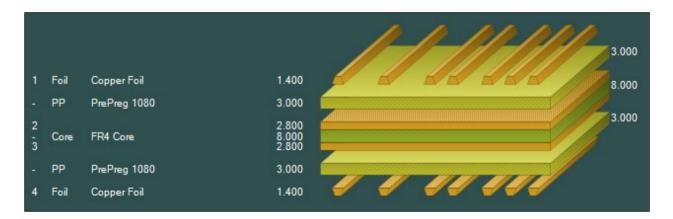

The Speedstack allows the user to view stackup in 2D or 3D format. Layer and material annotation is clear and easy to read and each layer may be selected and queried to display the associated material type and properties, including the associated data file. Visible drill information ensures that designers instantly know which layers support conventional, blind and buried vias.

Speedstack allows you rapidly to build and share stacks and verify via aspect ratios and track spacing rules. The stack file contains base material information combined with layer description and a complete listing of transmission line structures deployed in the stack. Keeping all stack

information in one file ensures that manufacturing data is accurately shared between original designer and fabricator.

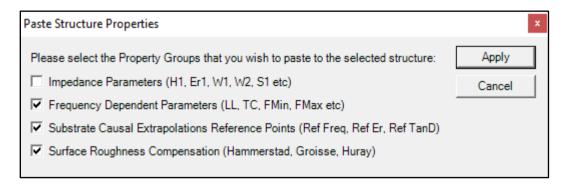

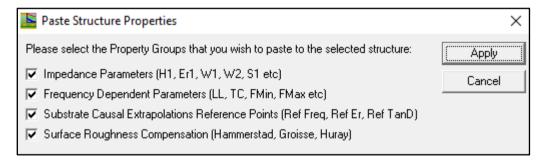

Speedstack's Stack Editor provides efficient and time-saving features such as Copy/Paste Material properties so the stack designer can copy all properties from a selected material and then paste user-selectable property groups to other materials.

Speedstack allows the designer to retain and re-allocate structures when changes are made to the electrical layers of the stackup. This enables reallocation of structures after the following stackup changes:

Adding and deleting foils and/or cores – increasing or reducing the layer count

Moving foils and cores – maintaining the layer count

Exchanging two different thickness cores within the stack

Copying and pasting foils or cores – increasing the layer count

# High quality documentation and file format

Speedstack saves the stack in efficient electronic format and outputs stack graphics in a variety of formats to suit your requirements. Stack data may be output in GERBER, DXF, BMP, JPEG, TIFF and XML. In addition, the stack data can be exported in comma-separated form for inclusion in other systems. Speedstack's high quality customisable printouts make it easy to discuss alternate builds and pricing impacts with fabricators.

Applications engineers, front end and production engineers benefit from receiving stack information in an intuitive, easy to understand format. The Speedstack .sci file contains full details of the layer stackup of a particular job. If changes are necessary or preferred stacks are to be shared with customers, Speedstack can cut the time for documentation and information sharing to a fraction of the time taken when employing traditional methods such as spreadsheet, word processor or presentation software.

# Integration with the Si8000m/Si9000e

Speedstack is fully integrated with the Polar Si8000m Controlled Impedance and the Si9000e PCB Transmission Line Field Solvers so the user can quickly add controlled impedance structures to layers in the stackup. The designer or board fabricator can use the Goal Seek facility of the Si8000m/Si9000e field solvers to arrive rapidly at the controlled impedance structure parameters to produce the target impedance.

# **Materials library**

The Speedstack supports a flexible materials library. This allows the designer to use standard materials data and also provides the facility to create new material libraries. PCB fabricators can also build libraries of commonly stocked materials to give interconnect designers visibility of the materials held in stock. Speedstack thus supports three types of library – custom user libraries of materials, generic designer libraries of materials of given dielectric characteristics (for example, thicknesses) along with a comprehensive set of materials libraries from PCB base material suppliers who are members of the Polar Speedstack Material Partner program.

# Online / on-premise materials libraries

The Speedstack Material Library includes an online library to allow users to download material library MLBX files from the Polar website. The online material libraries feature provides the user with a list of available library files; on selection the file is downloaded and is either appended to the existing data or replaces the existing data.

Speedstack also includes an on-premise option to allow for users who cannot connect to the online library due to network security restrictions

#### Speedstack's Virtual Material mode

Speedstack provides *Virtual Material* mode allowing you to build and experiment with stackups (for example to examine the effects on impedance structures of different trace widths or dielectric heights) without requiring real materials to be entered into a materials library.

In Virtual Material mode you will use the Stackup Wizard to enter a few details about the stack, the number of layers, overall board thickness, plane and mixed layers, etc., along with solder mask and copper thickness and build type (foil, core or HDI.) and drills Speedstack will then build a stack to the specified board thickness by equally distributing the dielectric regions. If a preferred core thickness is specified the software will maintain the dielectric thickness for core regions but then equally distribute prepreg regions to reach the target board thickness.

#### **Preferred builds**

PCB fabricators are able to create and share preferred builds and exchange the associated information with designers. Build data also includes blind and buried via specification. This simplifies the task of sharing stackup and drilling information between board shops and the design community.

#### Dimensional information

Finished board thickness is a critical dimension in many applications; Speedstack keeps track of the finished PCB thickness and tolerance and allows fabricators the flexibility of adding in-house post-press thickness for prepreg layers. Additionally, Speedstack takes into account plating thickness where appropriate.

# High layer count boards

On boards with high layer counts it can be very easy to make a change that would produce a non-symmetrical stack. The Speedstack Design Rules Check monitors symmetry across the stack, and ensures that material symmetry is maintained. Speedstack also makes it easy to set the symmetrical build mode to ensure that any changes you make are applied equally across the stack.

# Supplier management

When multiple-sourcing PCBs or when moving from prototype to volume production, the stack and fabrication design rule checks ensure that the manufacturing capabilities of your chosen suppliers are not overlooked. In addition the professional documentation output ensures that layer stack information is accurately conveyed to PCB suppliers.

# **Graphical interface**

Speedstack offers an easy to interpret graphical interface. Clearly showing the layers supporting blind and buried vias, Speedstack also records the data file for each layer (including ident and peelable mask layers). The graphical interface is especially designed to simplify the process of communication between interconnect designer and fabricator. OEMs who need to manage boards sourced from multiple suppliers will also find this facility invaluable. In addition to physical layers Speedstack adds mask and notation for electrical layers.

# Interfacing with other systems

Speedstack is able to load an XML file on launch. If an XML file (.stkx) filename parameter is specified on the command line it will import this file into Speedstack.

Speedstack can call an external program / utility / script via the External Utilities menu options. The menu items are configured within the Configuration option.

# Importing and exporting stackup information IPC-2581 Rev B

1PC-2561 Rev B

Speedstack incorporates Import from and Export to IPC-2581 Rev B option with interactive interface, supporting stack up material and structure information

#### Ucamco

Speedstack incorporates the facility to read in files in XML format and Ucamco Job File format, providing comprehensive integration with Ucamco and will import files from and export to both Ucam and Integr8tor.

#### 7uken

Speedstack integrates directly with the Zuken CR-8000 Design Force and Zuken Design Force DFM Center PCB manufacturing pre-processing and CAM system, simplifying material communication in the supply chain. Designers can define layers in DFM Center then export to Speedstack to define materials and provide a fully documented stackup in a format widely recognised by both PCB supply chain managers and fabricators.

Stacks may be exported to the Polar CGen Coupon Generator for subsequent processing into test coupons.

The Export CITS File option will create test files for Polar CITS controlled impedance test systems.

Speedstack can generate printed output in DXF, Gerber, CSV and XML, as well as graphic image formats JPEG, BMP and TIFF.

Export options also include Cadence Allegro, CSV, IPC-2581 Rev B and Mentor Graphics.

Import / export XML file formats support frequency dependent structure properties.

Converting imported electrical layers to cores

When importing stackup data from some CAD / CAM systems only the electrical layers are defined, so copper layers may appear adjacent each other. Speedstack allows conversion of two adjacent electrical layers into core or flexible core materials using the Convert to Core function.

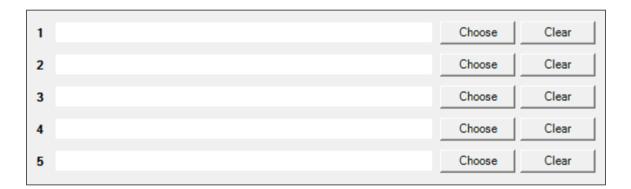

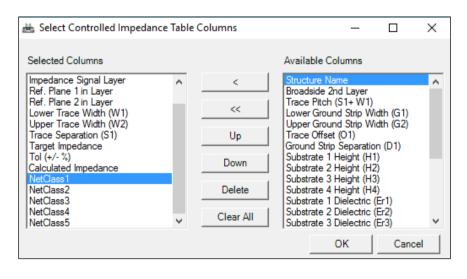

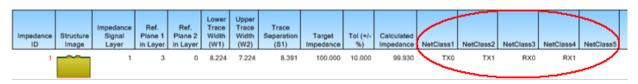

#### Structure net classes

Speedstack is able to import and store up to five net class names with each structure. These net class names provide a link to the matching impedance nets inside the ECAD PCB layout system.

# **Installing Speedstack**

# **Installing and activating Speedstack**

It will be necessary to install and activate the product license and set operating options prior to building stacks or performing calculations with Speedstack. See *Configuring Speedstack*|*Licensing* to select the associated field solver and purchased options.

# Obtaining a Speedstack license

Speedstack is license using the FlexNet Publisher licensing service. Contact <a href="Polarcare@polarinstruments.com">Polarcare@polarinstruments.com</a> for installation/activation directions.

Download the software from the supplied link. Unpack and save the installation file to a suitable folder then run Setup.

# Uninstalling the software

Caution: Prior to uninstalling, make a copy of the Speedstack folder structure and data files and store in a safe place.

To uninstall the Speedstack software:

Windows 7/8/10

Choose Settings|Control Panel; select Programs and Features and right click Speedstack and choose Uninstall.

# **Getting started with Speedstack**

# Online tutorial guides

Polar's web site provides online downloadable quick start and version specific user guides to familiarize users with the operation and features of the software.

From the Help menu choose Speedstack Help to download the Getting Started guide, along with tutorials for stack editing, managing materials libraries, manufacturing constraints and controlled impedance structures:

https://www.polarinstruments.com/help/speedstack/tutorials/

Download the user guide for your Speedstack version:

https://www.polarinstruments.com/help/speedstack/Nrmstart.htm

# **Stackup Templates**

Polar's web site provides online downloadable prebuilt sample templates and associated technical reports (suitable for Speedstack 2019 or higher) to familiarize users with the operation and features of the software.

https://www.polarinstruments.com/support/stackup/templates.html

The stackup templates listed include materials and drills are typical of standard stacks used in PCB construction and can be used as a starting point when building your own stacks. Stackup samples include core and foil build models in both material library and virtual library modes (see *Creating and editing stackups*) for rigid stackups, flex-rigid stackups and multiple press cycle HDI stackups.

Click on the link to the stackup template page and download the Speedstack template project (.sci) file; save to a convenient location and the use the Open Project command in Speedstack to view and edit the stackup. Note that the sample stackups are shown with dimensions in microns.

# **Using Speedstack Stackup Builder**

# Speedstack Stackup Builder

Double-click the Speedstack icon to start the Speedstack program and display the Stack Editor.

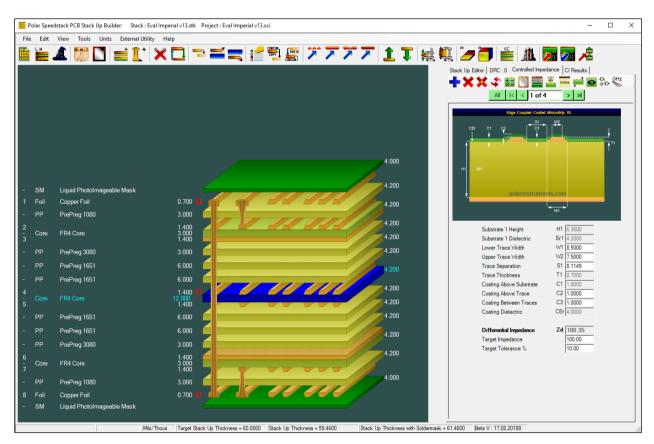

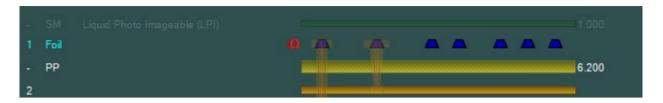

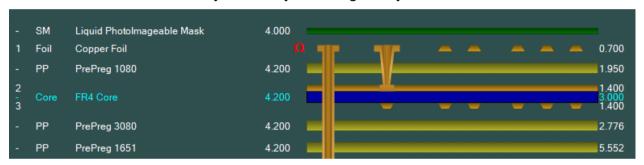

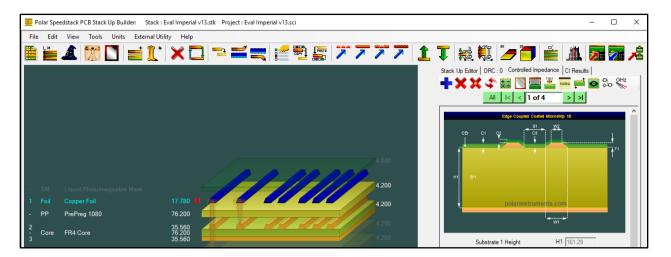

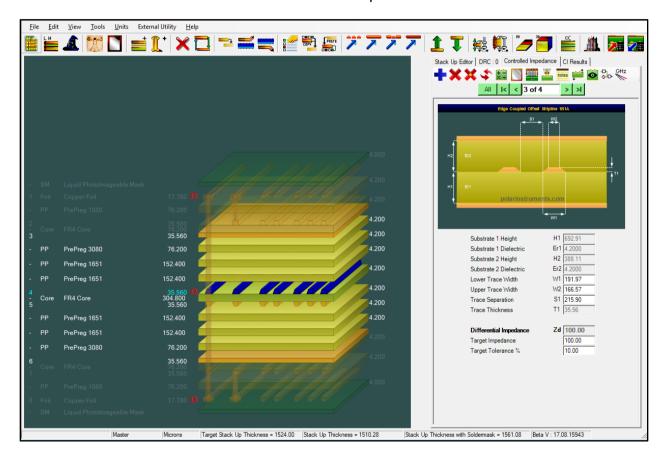

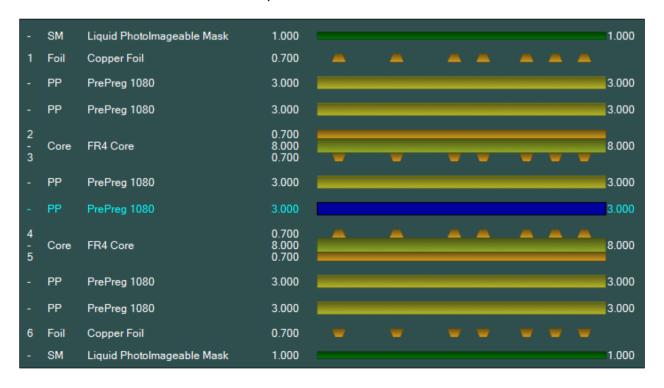

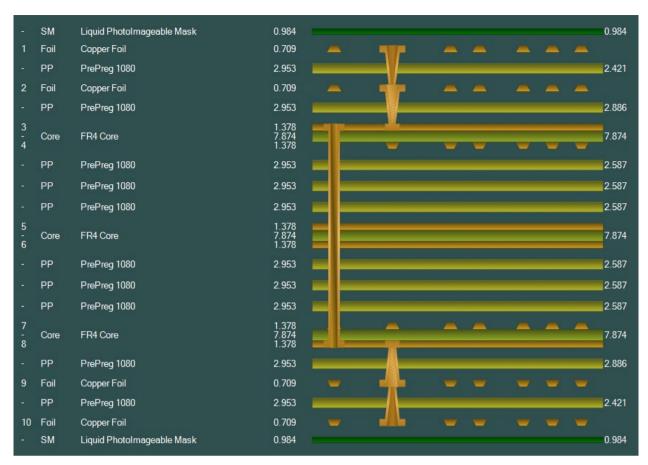

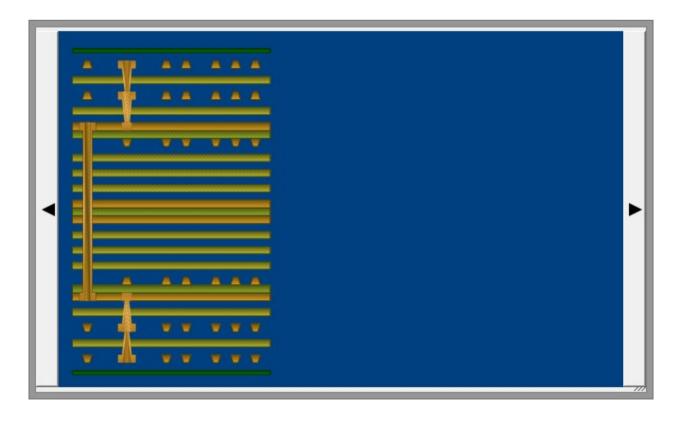

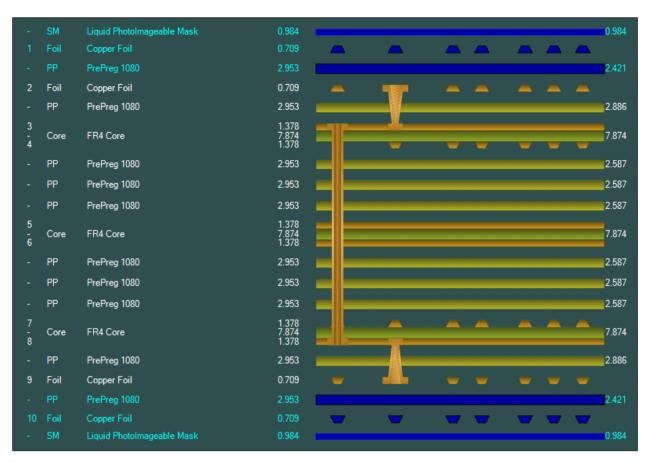

#### The Stack Editor

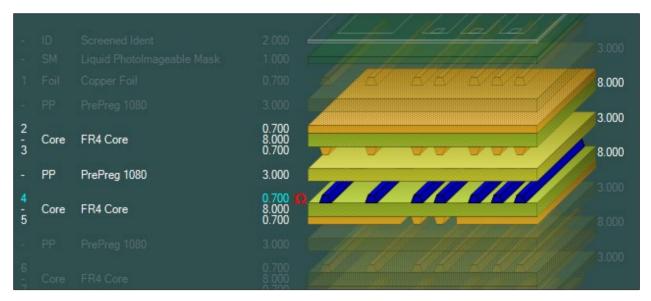

The Stack Editor screen displays all details of the stack, including copper and prepreg materials, solder masks and ident layers, drilling information, controlled impedance structures and design rule check results.

Controlled impedance structure data may be transferred between Speedstack and the associated Polar Si8000m or Si9000e field solver to goal seek for the target structure dimensions.

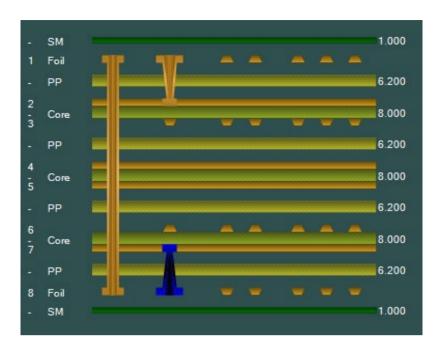

The Stack Editor screen

The Speedstack Stack Up Editor screen comprises:

- The Menu bar drop-down context sensitive menus containing all the Speedstack Editor commands

- The Tool bar incorporating short cut tool buttons to the most common menu commands

- The Stackup Build and Construction Window where the board stackup is built and edited

- The Controlled Impedance window displaying the controlled impedance structures (if any) for the selected layer.

- Stack Up Editor/Notes tab— a free form text area for explanatory or commentary notes

- Design Rules Check (DRC) tab allows design rules and manufacturing constraints to be specified and violations displayed

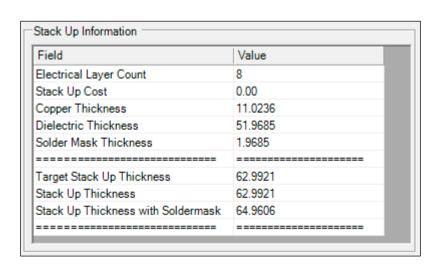

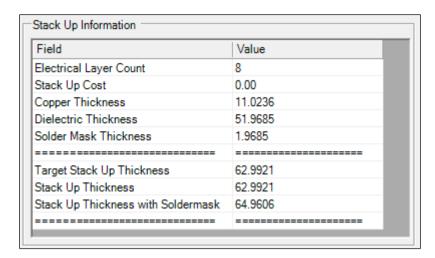

- Stack Up Information properties area table containing information related to the whole stackup

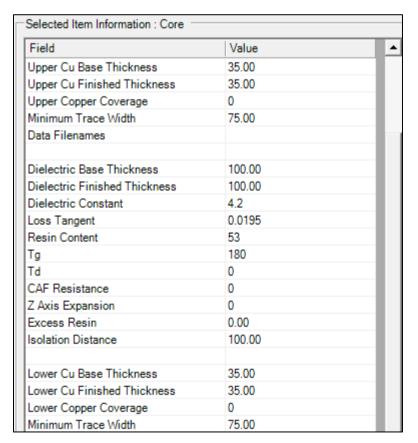

- Selected Item Information area properties table containing the attributes of the layer currently selected in the stackup

- The Controlled Impedance Results tab summarizing the controlled impedance structures within the stack

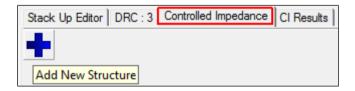

# Controlled Impedance window

The Controlled Impedance window displays all the controlled impedance structures and associated parameters for the selected layer.

Step through the structures with the structure browse control – structures with the impedance within tolerance are shown in green, structures where the impedance is outside the specified tolerance range are shown in red.

# The Speedstack menu system

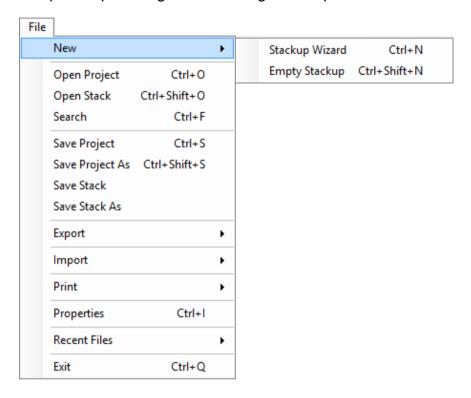

#### The File menu

The File menu allows for creation of new stackups and projects and opening, saving, printing, importing and exporting existing stackups and projects and data files from companies providing data exchange with Speedstack.

# Opening projects

Stackups that incorporate controlled impedance structures are saved as projects. Click Open Project and navigate to the project folder; projects are saved as .sci files. The stackup along with all its design rule checking settings and controlled impedance information is loaded.

# Saving stackups

Click the Save button to save the stackup. Users are recommended to save the stackup frequently during the stackup creation process to avoid data loss; stackups are saved as .stk files.

#### Saving projects

Use the Save Projects command to save a stackup and its controlled impedance structures.

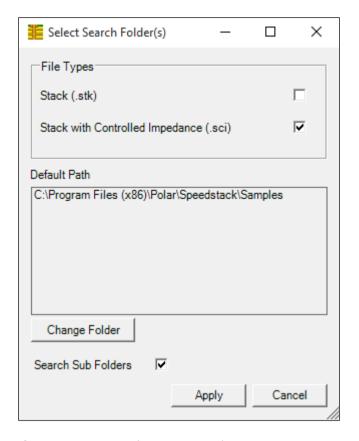

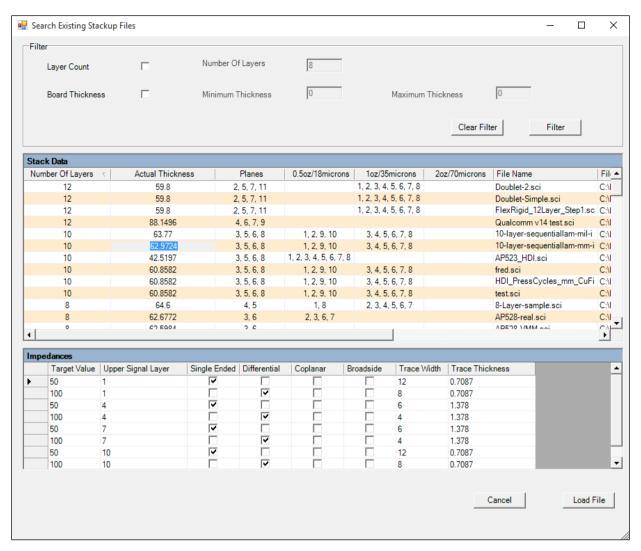

# Searching for stackups and project files

When creating new stackups and projects it will often be found convenient and timesaving to reuse an existing stack or project, modifying as required and the saving as a new stack or project. From the File menu choose Search and click Change Folder to navigate to the collection of stacks.

Choose from stacks and/or projects (stacks with controlled impedance;) with the folder chosen, click Apply.

# Supplying search criteria

The stackups and projects within the chosen folder structure are displayed. If appropriate supply criteria, layer count, board thickness, etc. and click Filter.

Step through the list, choose the matching stack or project and click Load File.

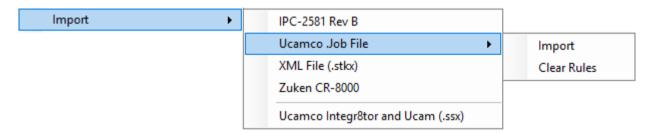

# **Importing Stackup information**

Speedstack incorporates the facility to read in files in:

IPC-2581 Rev B format

Ucamco Job File format

XML format

Zuken CR-8000 format

Ucamco Integr8tor and Ucam format

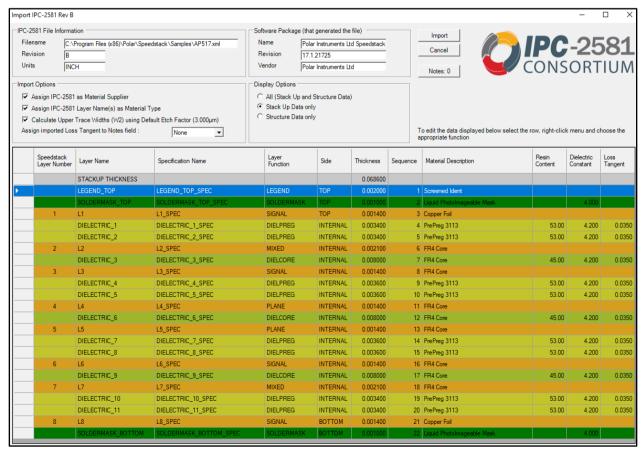

#### IPC-2581 Rev B

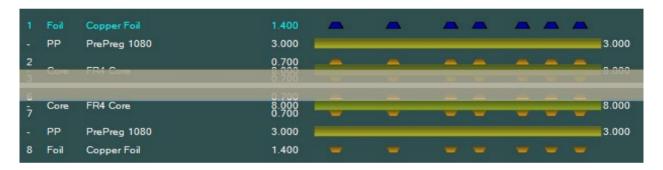

Speedstack can import stack up and impedance structure data using the IPC-2581 Rev B XML file format. Use the IPC-2581 Rev B command to import IPC-2581 Rev B (XML) files using the interactive interface. The stack shown below displays both stackup material and structure information. The foil, prepreg, core and solder mask material data grid colours are determined by the Speedstack Configuration,

The dialog above provides user guidance through the import process.

The IPC-2581 File Information pane displays useful file data including the file name, revision and units. IPC-2581 supports inches, millimetres and microns.

The Software Package pane details the application (including the revision and vendor) that generated the IPC-2581 file.

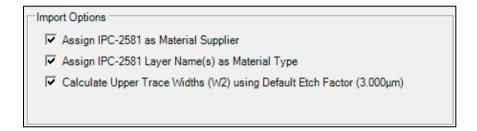

# Setting import options

Set the import options to control how the IPC-2581 data is allocated in Speedstack:

The material type can optionally be derived from the layer name and the upper trace width can be derived from the given trace width and default etch factor.

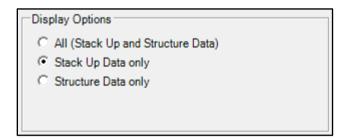

# Setting display options

From the Display Options dialog pane choose to display all data or stackup or structure data only

#### Sorting layer information

The stackup imported from the IPC-2581 file is shown in data grid form. Data can be sorted by column – click on each column header to sort in ascending or descending order by sequence, layer number, layer name, etc.

# Assigning layer functions

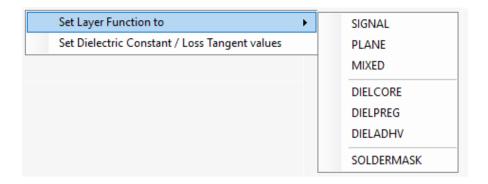

During the import process it may be necessary to consult the board authority or design documentation to ascertain the function of each layer, signal, plane, dielectric, core, etc.; the Layer Function determines the layer / material type.

Right click each layer and use the Set Layer Function to assign the layer its designated function.

# Setting loss values

Dielectric constant and loss tangent values can be set for each layer; select the layer (it will highlight in blue) and then right click the layer, the dialog should show the current values; enter each value and click Apply.

With all the editing completed, click Import to bring the file into the Speedstack Editor.

The imported stack can be processed using the Speedstack editing functions.

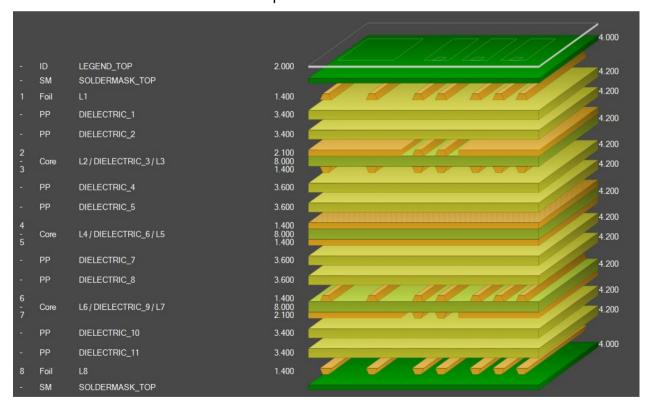

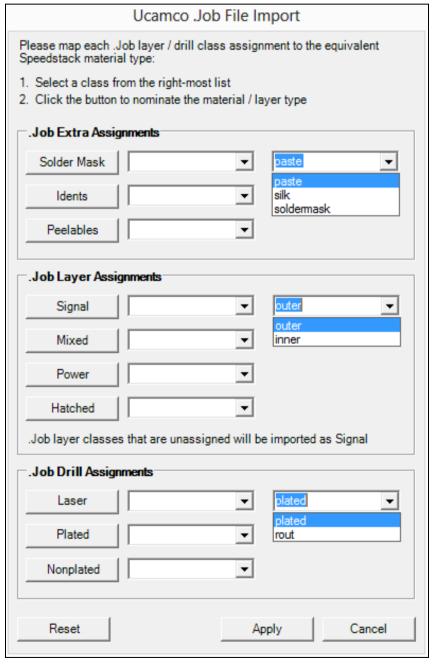

#### Ucamco Job Files

The .Job file format contains a varying amount of stackup information depending upon the how the system has been configured by the Ucam user.

Speedstack will import files from both Ucam and Integr8tor.

Choose File|Import|Ucamco Job File|Import and select the .job file and click Open. The Ucamco .Job File Import dialog is displayed:

The .Job file contains user-definable material / drill class definitions so it will be necessary to map these definitions to the various Speedstack material and drill types.

To apply assignments select the class from the drop down list then click the associated button to nominate the material or layer type. Click Apply.

Note: Where stack data are not included in the .job file it will be necessary to include or update properties (for example, solder mask properties such as thickness and dielectric constant) before adding impedance structures.

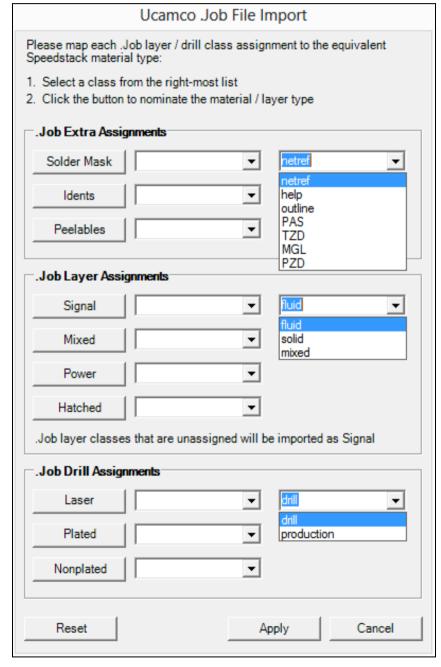

# Integr8torJob files

When Integr8tor files are imported the Ucamco .Job File Import dialog is displayed as shown below.

Select the assignment options as described above and click Apply. Click Reset to clear the assignments.

#### Clear Rules

The Clear Rules command will delete all previously learned rules.

#### XML files

Choose File|Import|XML File (.stkx), select the .stkx file for import and click Open.

#### Zuken CR-8000

Choose File|Import|Zuken CR-8000 format, select the .stkx file for import and click Open.

Ucamco Integr8tor and Ucam format (.ssx)

Choose File|Import|Ucamco Integr8tor and Ucam format, select the .ssx file for import and click Open.

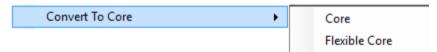

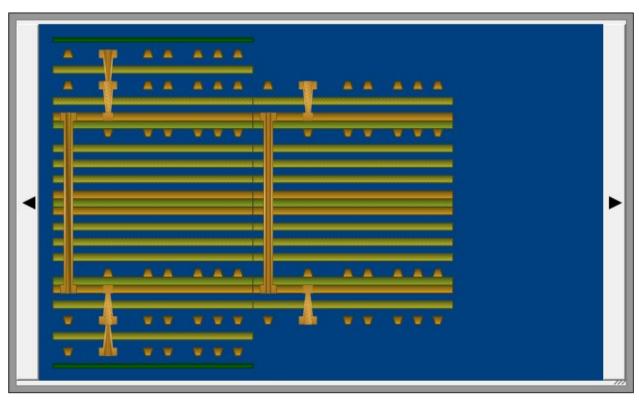

# Converting imported electrical layers to cores

When importing stack up data from some CAD / CAM systems only the electrical layers are defined. In this case copper layers may appear adjacent each other in the Stackup Editor. Speedstack allows the user to quickly convert two adjacent electrical layers into Core or Flexible Core materials using the Convert to Core function.

Select the adjacent layers within the stack – Speedstack adds the Convert to Core command to the Edit menu.

Select the Core type – Speedstack displays the core library; select the core – the layers are converted into the selected core; note that when converting two foils to a single core material the lower copper trace will be shown inverted.

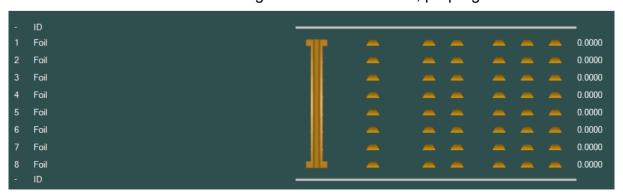

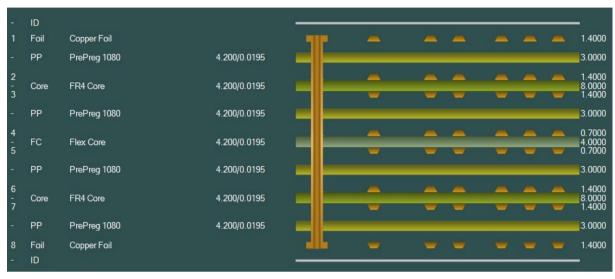

Consider the stack below. Using 'Convert to Core' alongside other Speedstack editing functions, an electrical layer only stackup can be converted into a useful fully defined stackup containing full definitions of foils, prepreg and core materials.

Add a prepreg layer between layers 1 and 2.

Repeat for layers 3 and 4, 5 and 6 and 7 and 8.

Select layers 2 and 3 and convert to a core.

Repeat for layers 4 and 5, 6and 7.

The resulting stack should appear similar to the stack below.

# **Exporting stackup information**

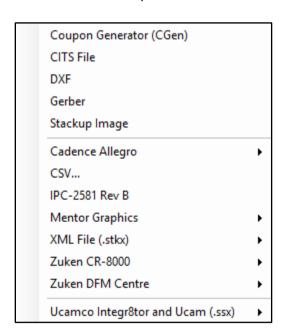

Speedstack incorporates the facility to export stack data to external programs. From the File menu choose Export and choose the format from the Export sub-menu.

Exporting to Coupon Generator (CGen)

Stacks may be exported to the Polar CGen Coupon

Generator for subsequent processing into test coupons. Click Export To | Coupon Generator – open the file in CGen.

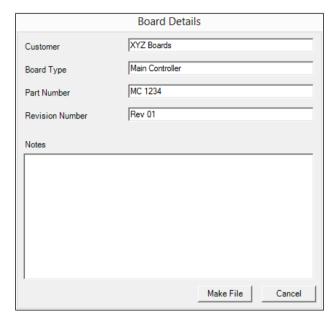

# Export CITS File

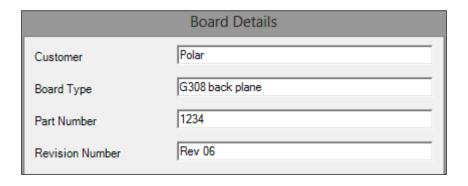

Use the Export CITS File to create test files for Polar CITS controlled impedance test systems. Supply board details via the Board Details dialog.

Click Make File to generate .cif files (CITS test files).

# Generating printed output

Speedstack can generate printed output in DXF, Gerber, CSV and XML, as well as graphic image formats.

# DXF, Gerber, CSV and XML files

Choose DXF..., Gerber..., CSV... or XML File and navigate to a suitable folder, name the file as appropriate and save.

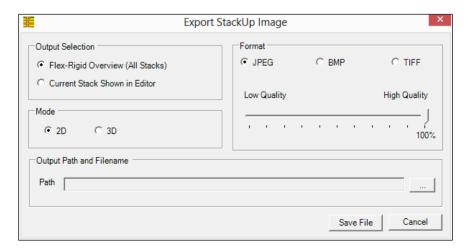

#### Stackup images

Speedstack can export stackup images in JPEG, BMP and TIFF file formats. Select from 2D or 3D displays.

The Low Quality – High Quality slider specifies JPG quality.

Choose the Flex-Rigid Overview (if appropriate) to display the master stack and associated sub-stacks or Current Stack Shown in Editor. Specify the destination folder and file name and save.

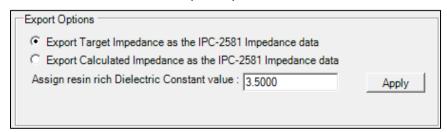

# Cadence Allegro (IPC-2581 Rev B)

Speedstack supports reading/writing in IPC-2581 Rev B formatted data. Choose the Cadence Allegro/IPC-2581 Rev B option and supply the file name and destination folder: the Export IPC-2581 Rev B dialog is displayed.

## Choosing export options

Use the dialog to modify, if necessary, the file information details and choose the export options.

Specify whether Speedstack's target or calculated impedance is to be used to populate the IPC-2581 file.

Supply a value for dielectric constant and click Apply. Click Export.

# Mentor Graphics

Choose the Mentor Graphics option, choose the file version and supply the file name and destination folder. (Note the .ssx file extension.)

#### Zuken CR-8000/DFM Centre

The Zuken CR-8000 and DFM Center PCB manufacturing pre-processing and CAM systems integrate directly with Polar Instruments' Speedstack PCB system. Choose the file version, navigate to a suitable folder and save the file (XML format).

# Ucamco Integr8tor and Ucam

Choose the Ucamco Integr8tor and Ucam option and file version and supply the file name and destination folder. (Note the .ssx file extension.)

# Assigning properties to projects and stackups

The stack file Properties dialog may be displayed automatically each time a new stackup is created (see Tools|Options|General) and provides a range of text fields for descriptive information, e.g. stackup author, company name, file create date, stackup name, version, etc.

From the File menu choose the Properties command to add descriptive text fields — information contained in the Properties dialog will be displayed on stackup printouts.

To display the Properties dialog each time a new stackup or project is created, from the Tools menu choose Options and click the check box below on the General tab

✓ Display File Properties Dialog for New Stackups and Projects

## Backing up stackups and libraries

It is strongly recommended that stackup files (assigned the .stk extension), project files (assigned the .sci extension) and library files (assigned the .mlbx extension) be backed up to a secure location.

#### Opening recent files

Click Recent Files to select and open a file from the most recently used file list.

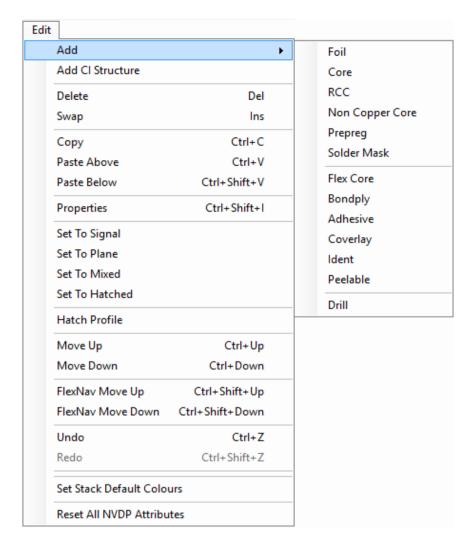

#### The Edit menu

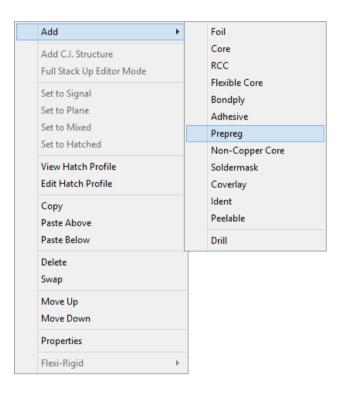

The Edit menu contains the commands necessary to create and modify board stackups. The designer or fabricator works within the free-form stackup build and construction window and in Materials Library mode adds layers of foil, core, prepreg, etc., from the materials library.

## Material Library and Virtual Material modes

Speedstack provides the option to switch easily between Material Library and Virtual Material modes allowing the stack designer to build and experiment with stackups (for example, to examine the effects on impedance structures of different trace widths or dielectric heights) without requiring real materials to be entered into a materials library.

Controlled impedance structures can be added to the stack. When Add CI Structure is selected Speedstack switches to the Controlled Impedance pane and allows the designer to add structures appropriate for the selected layer. The items that can be edited depend upon whether the Stack Up Editor or Controlled Impedance tab is selected.

Layers can be changed to signal, plane, mixed or hatched, moved up or down or copied and pasted, or assigned properties as required.

Use the Delete and Swap commands to delete materials or swap materials from the Materials Library.

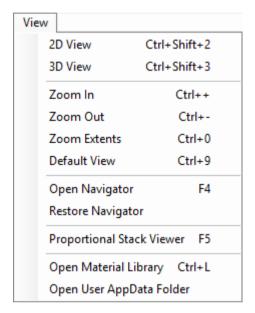

#### The View menu

Use the View menu to change the Stack Editor display whilst adding or removing materials or modifying or refining the stack.

The View menu allows Speedstack to display the stackup in a 2-dimensional or 3-dimensional aspect.

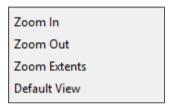

Zoom In to get a close-up view of the stack or Zoom Out to see more of the stack at a reduced size. Zoom Extents will adjust the zoom level to display the whole stack.

Hint: Click the mouse centre button/wheel to Zoom Extents.

With the Flex / HDI option installed choose the Open Navigator command to view the master and associated substacks. The floating Navigator window may get covered by other application windows when switching between programs; – use the Find Navigator to display a reduced Navigator window at the top left screen corner.

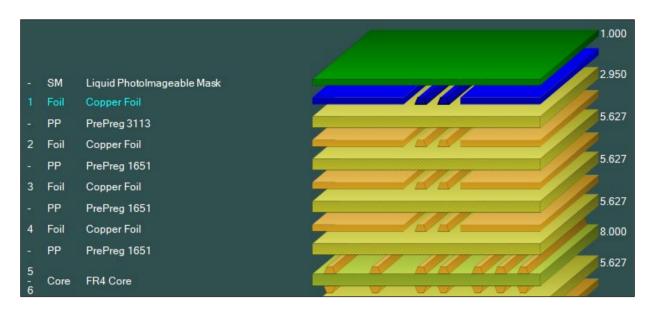

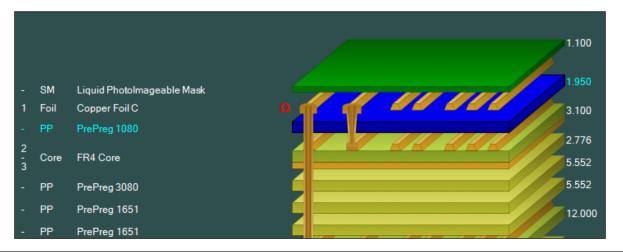

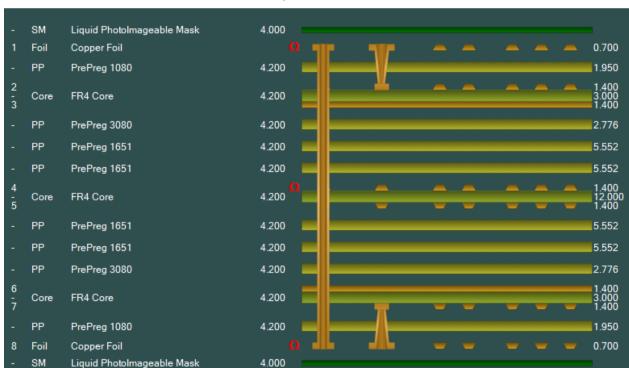

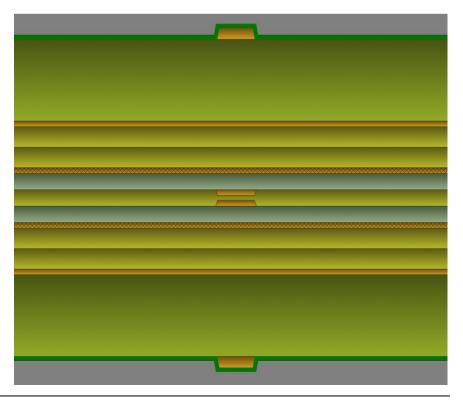

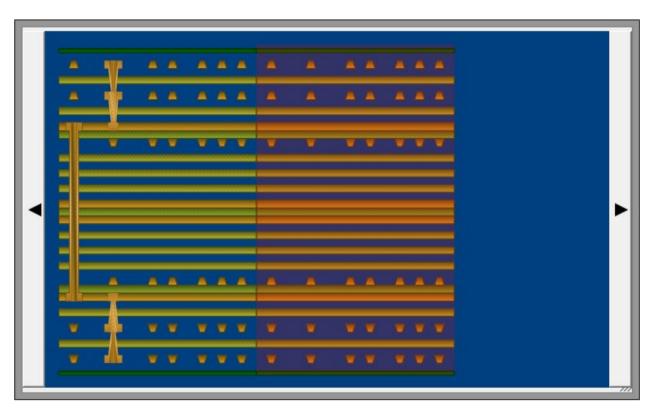

# Proportional Stack Viewer

Use the Proportional Stack Viewer to display the stack currently selected in the Stack Editor so the material thicknesses are shown proportional to each other. This can be informative as a visual aid, especially when considering the dielectric thicknesses between electrical layers.

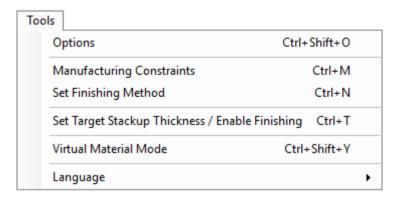

#### The Tools menu

Use the Tools menu to configure Speedstack.

The Options command displays the configuration options, manufacturing constraints, target stack thickness and finishing options. See *Configuring Speedstack* for details.

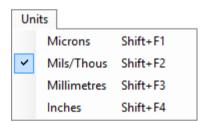

#### The Units menu

Use the Units menu to select the stackup units, Microns, Mils/Thous, Millimetres or Inches

### **External Utility**

Use the External Utility commands to start a program external to Speedstack. The programs are defined in the Configuration Options|External Utilities dialog.

### The Help menu

Use the Help menu commands to access the User Guide for the current Speedstack version or tutorials relating to common Speedstack operations.

Review the licensing terms with the License and About Speedstack commands.

# **Configuring Speedstack**

When first run, the Speedstack environment is initialised to its factory settings. These may require adjustment before outputting a finished stackup and/or project. Default settings are changed using Tools|Options, Tools|Manufacturing Constraints and Tool|Set Finishing Options.

# **Environment and default settings**

From the Tools menu choose the Options command to display the Configurations Options dialog.

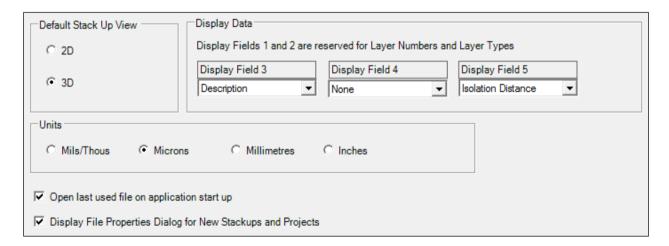

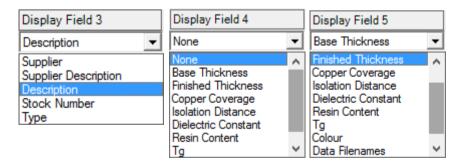

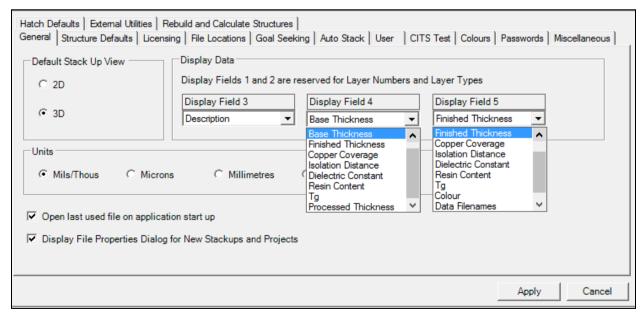

# General Options

Choose the Default Stackup View – 2D or 3D; select the data fields that will appear alongside the stack in the Stack Editor

Choose the stackup units; Speedstack supports Mils/Thou, Microns, Millimetres and Inches. Click the Open last used... check box to specify that Speedstack should open the last used file on start-up.

Note: Processed Thickness is the Finished Thickness for copper layers and Isolation Distance for dielectric layers.

Clicking the Display File Properties Dialog... will display the File Properties Dialog each time a new stackup or project is initiated.

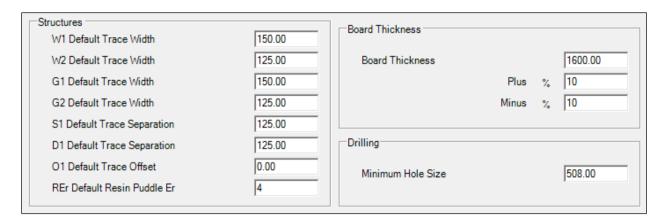

#### Structure Defaults

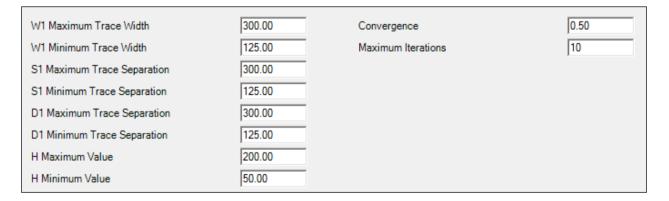

When adding new controlled impedance structures default values are entered for the trace widths and separations. Use the Structure Defaults tab to specify the default structure parameters, board thickness and minimum drill hole size.

# Licensing

Use the Licensing tab to tick the purchased licensing options.

○ Speedstack License Only

○ Enable Speedstack PCB and Si8000m link

⑥ Enable Speedstack Si and Si9000e link

License Options:

☑ Speedstack Flex / HDI License (SF)

☑ Hatch Mode License (XFE)

☑ Speedstack Import / Export License (IO)

☑ Speedstack / Ucamco Integration License (UCAMCO)

To activate the Speedstack controlled impedance function, ensure that the Si8000 or Si9000 is installed; from the Licensing tab choose either Use Polar Si8000m License or Use Polar Si9000e License option as appropriate.

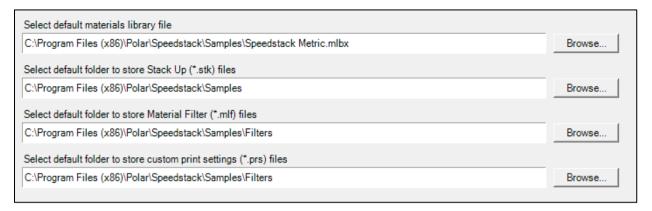

#### Choosing default file locations

Use this dialog to choose which materials library the Speedstack uses at start-up. Click the File Locations tab and use the Browse button to navigate to the library (.mlbx) file.

The File Locations tab provides for default locations for stackup or project files, Material Filter (.mlf) files and custom print settings (.prs) files. Browse to the target folders and click OK to confirm (create new folders if necessary).

# Specifying goal seeking parameters

Click the Goal Seeking tab to specify the default values for trace widths and separations used during goal seeking.

During goal seeking the calculated value for impedance will progressively converge upon the target value.

In the Convergence text box specify the difference between the target impedance and the actual impedance at which goal seeking will terminate.

Use the Maximum Iterations text box to limit the number of iterations used during goal seeking.

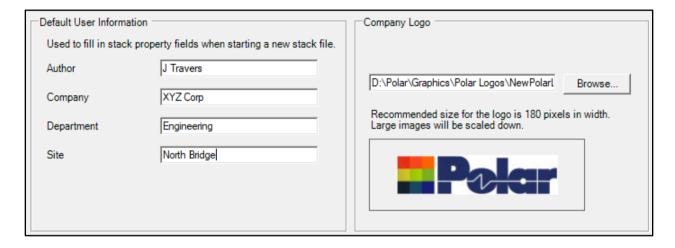

# Setting user defaults

Information added to the User tab will be transferred to the File Properties dialog and used on printouts

Enter information as appropriate into the associated text fields; optionally, select a graphic for use as the company logo — optimum graphic size is 180 x 32 pixels — the graphic is printed in the preview box.

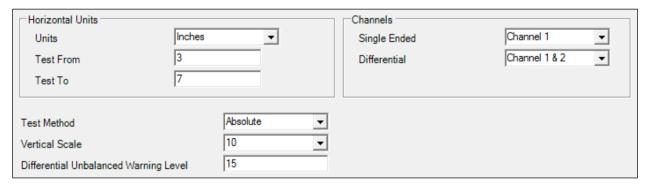

Specifying default CITS test file parameters

Speedstack allows the user to generate a CITS test file for each controlled impedance structure within the stack.

Select the CITS Test tab to specify the default test parameters to be used when initiating a CITS test file.

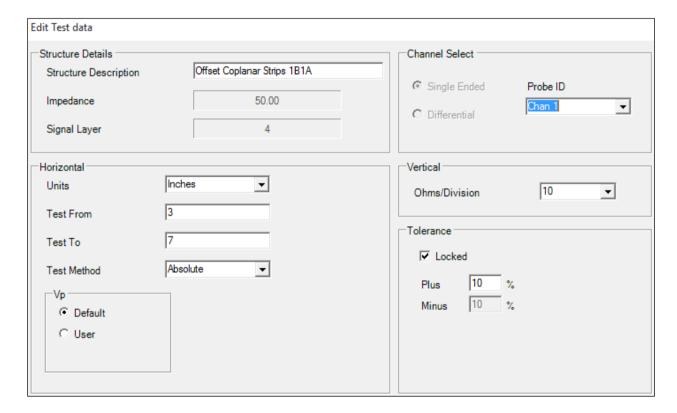

Each test file contains the test parameters (test units, distance, number of channels, etc.) to be used when testing the stack's controlled impedance structures using a Polar CITS (Controlled Impedance Test System). The test file may be edited via the Edit Test Data dialog.

#### CITS test methods

Note that the preferred test method is **Absolute**

The **Average** method should only be used with the express approval of the specifying authority.

See Polar Application Note AP8515 – CITS Test Methods

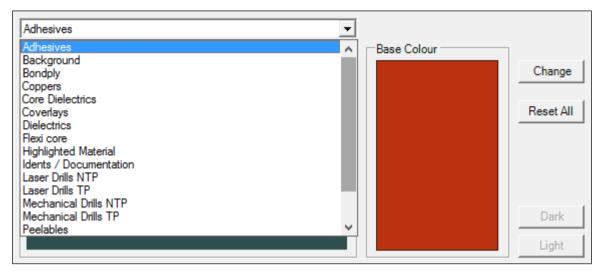

Choosing background and stackup layer colours Choose the Colours tab to change stackup component colours from their factory defaults.

Click Reset All to return to cancel changes.

# Miscellaneous Options

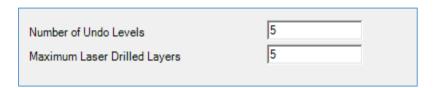

Use the Miscellaneous tab to specify the maximum Number of Undo for editing actions; choose the number of levels of editing Undo and the maximum number of layers a laser drill can span. (Exceeding this number will produce a Drill not Valid error message.)

# Hatch Defaults

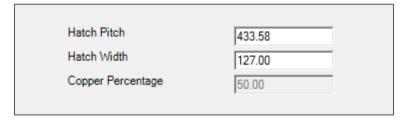

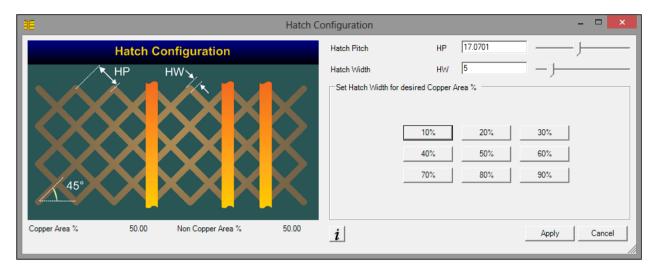

Use the Hatch Defaults tab to specify the default values for Hatch Pitch and Width and Copper Percentage when setting a plane to hatched (see Hatch Configuration.)

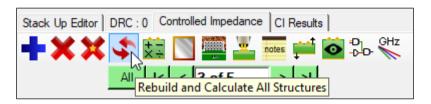

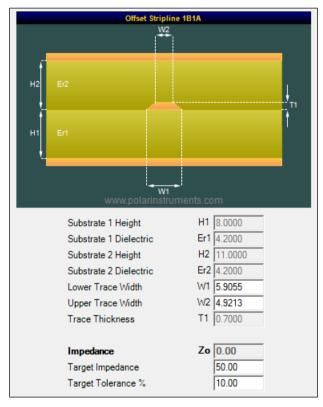

#### Rebuild and Calculate Structures

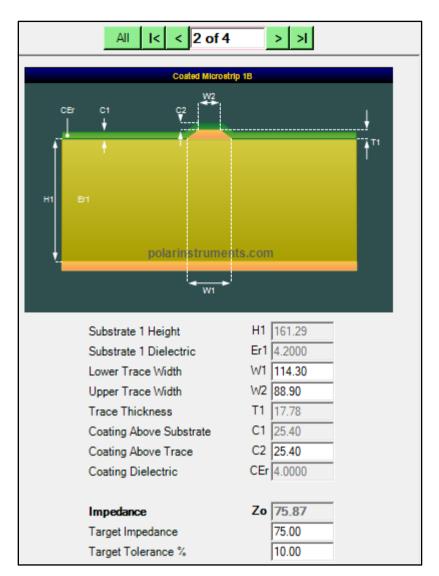

These options control the way that the Controlled Impedance structure parameters are updated from the stack up. When new structures are added or the Rebuild and Calculate option is selected, Speedstack will update all structures based on the selections below. Default: All options selected.

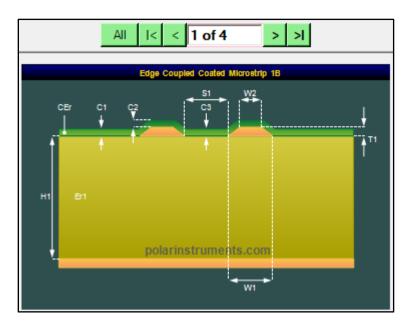

Substrate Height (H n)

Substrate Dielectric (Er n)

Trace Thickness (T1)

Coating Above Substrate (C1)

Coating Dielectric (CEr)

The Rebuild and Calculate Structures tab allows the designer to specify which parameters are included when controlled impedance structures are recalculated after modifying the stack.

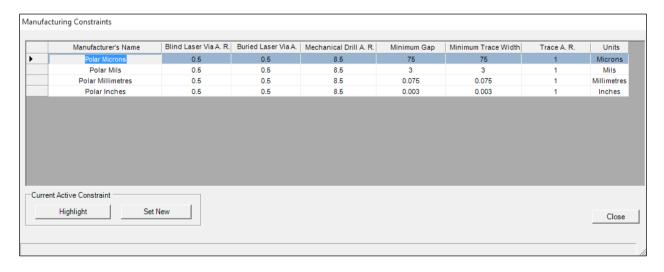

# **Manufacturing Constraints**

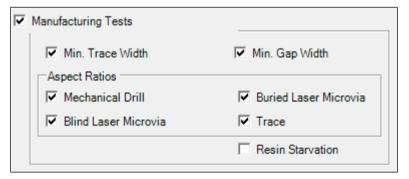

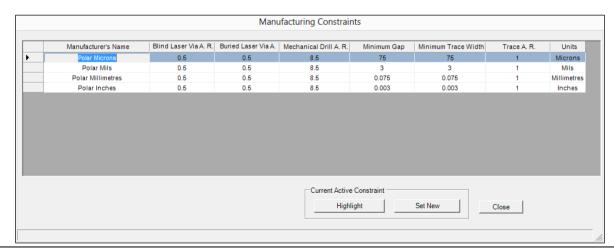

The Manufacturing Constraints options consist of a collection of manufacturing capabilities, minimum gaps and trace widths, buried and blind via and trace aspect ratios, drill aspect ratios, etc. that can be applied during design rule checking (see the DRC tab detail below.)

They will normally refer to differing levels of technology offered by one or more PCB manufacturers for a range of prices. The required information (shown in the example below) can normally be obtained from the manufacturer.

Click the Highlight button to highlight the current active constraint; to apply a new constraint select the constraint row and click Set New.

# Editing and adding constraints

To modify a constraint or add a new constraint, double click within the constraint row to be edited.

Modify each setting as required; click Done to confirm the settings and close the dialog.

To add a new constraint click the Add button, fill in the settings fields and click Done to finish. The new constraint will be added to the table of current constraints. Click the Delete button to remove the constraint from the list.

# **Set Target Stackup Thickness/Enable Finishing**

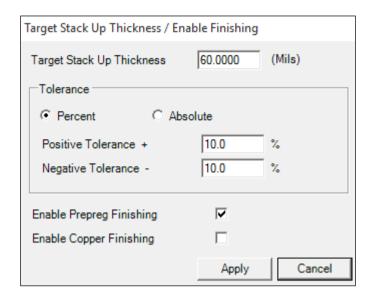

Set the Target Stackup Thickness and tolerances via the dialog below.

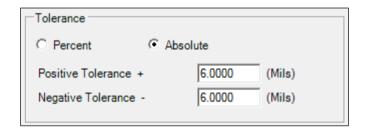

Tolerance may be set in terms of percentage or absolute values:

Note that positive and negative tolerance values can be set independently. The values should reflect the currently selected units.

To enable prepreg and/or copper finishing tick the associated check boxes. Click Apply.

Note: Unchecking the Enable Finishing options disables the Apply and Reset Finishing buttons. Note that these buttons are only available in Materials Library Mode – they are disabled in Virtual Material Mode.

# **Finishing Options**

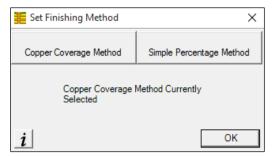

From the Tools menu choose the Set Finishing Method command to display the set finishing corrections dialog. Speedstack offers two methods: Copper Coverage Method and Simple Percentage Method.

Each method requires that the amount of copper to be added where plating is required be set. In addition, where the Excess Resin design rule check is used the minimum acceptable value must be set.

### Simple Percentage Method

Use the Simple Percentage Method to set the percentage of prepreg base height, which will be used to determine the isolation distance. The percentage is set for each electrical layer type pair.

Specify the IPC-6011 Class and plating thickness.

# Copper Coverage method

The Copper Coverage method allows the user to specify the amount of copper that will be embedded into the prepreg.

This can be set as a single value for each electrical layer type. Alternatively the amount of copper embedded will be calculated on an electrical layer by layer basis dependent upon the copper coverage for the layer set in the properties window. The greater the copper coverage the smaller the amount of copper that is embedded.

Specify the IPC-6011 Class and plating thickness.

Note: The two methods of finishing are not compatible with each other. The Copper Coverage method requires that the finished thickness of prepregs be entered in the library; that value stays locked in the stack unless the Simple Percentage method is set up; if Reset Finishing is then clicked the finished thickness reverts to the base thickness.

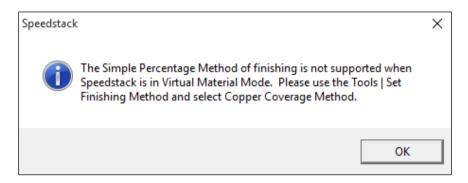

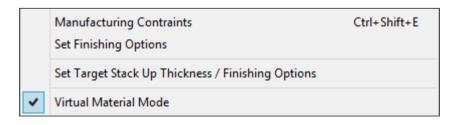

#### Virtual Material mode

The Virtual Material Mode command toggles between Virtual Material and Material Library modes.

Note: Switching to Virtual Material Mode disables the Apply and Reset Finishing buttons.

Note: Virtual Material mode and the Simple Percentage method of finishing are not compatible. Speedstack displays the message below if the two are selected simultaneously.

# Working with external utilities

Speedstack can call an external program / utility / script via the External Utilities menu options. The menu items are configured via Configuration Options|External Utilities.

To specify a program click Choose and navigate to the program and click Open. The program will be added to the External Utility menu.

# The Speedstack toolbar

The Speedstack toolbar comprises shortcut links to the most popular commands.

Note: toolbar buttons will be enabled/disabled depending on whether Speedstack is performing stack editing or controlled impedance calculations. Pause the mouse over each tool button to display the tool's screen tip

#### File operations

Create new stackup

Library mode

Virtual Material mode

Stackup Wizard

# Stack building operations

Symmetrical Mode off

Symmetrical Mode on

Mirroring Mode

Add layer to the stackup

Click to select the layer type. The list of layer types is displayed in the associated sub-menu.

Layers available include:

Foil Add foil layer to the stackup

Core Add core layer

RCC Add resin coated copper layer

Non-Copper Core Add non-copper core

Prepreg Add prepreg layer Soldermask Add solder mask

Flexible core Add flexible core layer

Bondply Add bond ply adhesive

Adhesive Add Adhesive

Coverlay Add coverlay layer

Ident Add screened ident layer

Peelable Add peelable mask

Add mechanical/laser drill between layers

# Editing the stackup

Delete selected stackup material or drill

Swap selected material

Note: the Copy and Paste buttons below are only enabled for the Stack Editor and DRC tabs – they are disabled for the Controlled Impedance and CI Results tabs.

### Copying and pasting materials

Copy material of the selected layer

Paste material above selected layer

Paste material below selected layer

Copy material properties

Paste material properties

# Changing plane types

Set the selected electrical layer as a signal layer

Set the selected electrical layer as a plane

Set the selected electrical layer as a mixed signal/plane layer

Set the selected electrical layer as a hatched plane

Note: the Move Selected Layer buttons below are only enabled for the Stack Editor and DRC tabs – they are disabled for the Controlled Impedance and CI Results tabs

Move selected layer up one layer

Move selected layer down one layer

Display properties dialog for the selected layer or drill

Note: the Apply and Reset Finishing buttons below are only enabled for the Materials Library Mode with the Prepreg and Copper Finishing Options checked (see Set Target Stack UpThickness/Finishing Options) – they are disabled for the Virtual Materials Mode.

# Applying finishing

Apply finished thickness

Reset finished thickness

# Changing the stackup view

Display 2-dimensional view

Display 3-dimensional view

**Proportional Graphics View**

# Managing the materials library

Go To/Display materials library

Exchanging data with the Si8000m or Si9000e Field solver

Copy controlled impedance data to field solver

Paste controlled impedance data from field solver

Copy to Si8000m or Si9000e Project

# **Creating and editing stackups (Virtual Material mode)**

Material Library and Virtual Material modes

Speedstack provides the option of switching easily between

Material Library and Virtual Material modes, allowing the

stack designer to build and experiment with stackups without

requiring real materials to be entered into a materials library.

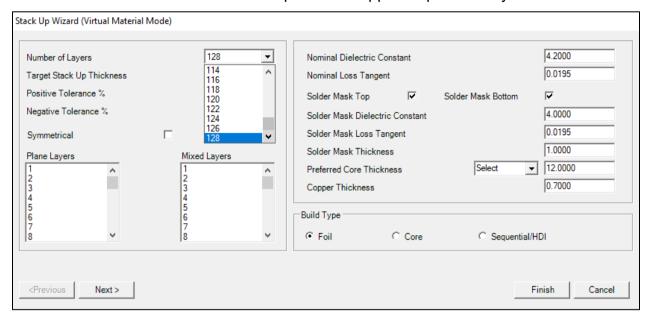

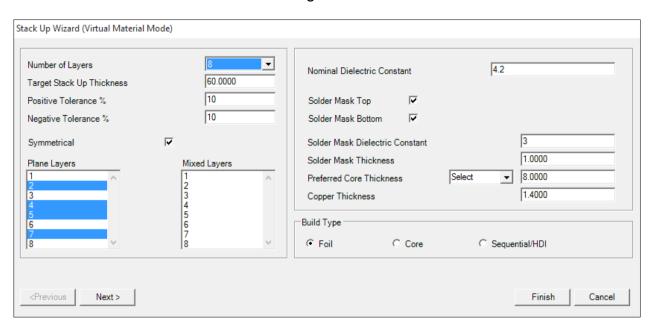

In Virtual Material mode the Stackup Wizard allows rapid entry of stack details, the number of layers, overall board thickness, plane layers, solder mask and copper thickness. Speedstack will then build a stack to the specified board thickness by distributing the dielectric regions equally. If a preferred core thickness is specified Speedstack will maintain the dielectric thickness for core regions but equally distribute prepregs to reach the target board thickness.

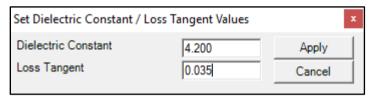

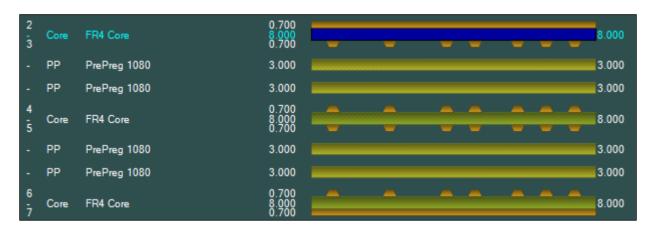

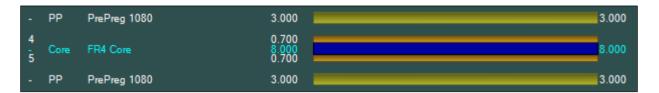

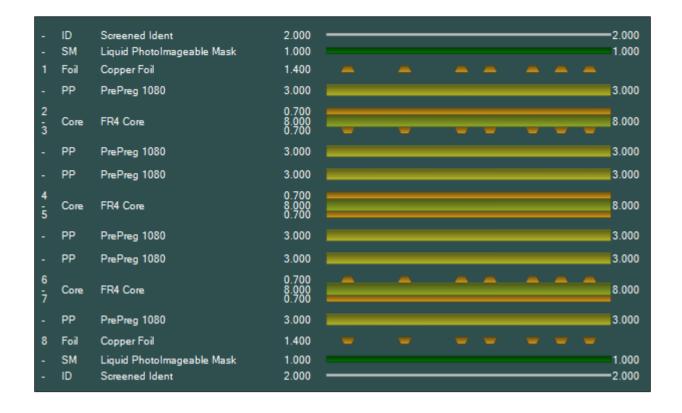

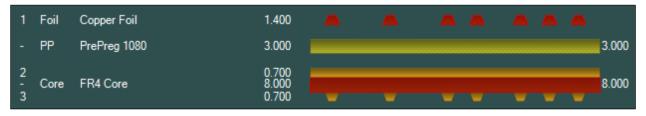

This section will describe the steps to construct an 8-layer, symmetrical FR-4 stack to the specification below using Speedstack's Virtual material Mode.

Thickness: 60 mil Signal layers: 1, 3, 6, 8 Plane layers: 2, 4, 5, 7 Fr· 42 Preferred core thickness: 8 mil 1 oz. / 1.4 mil Copper (all layers): LPI Mask: 1 mil PTH drill passes: Layers 1 – 8 Laser microvia passes: Layers 1 - 2, 8 - 7Impedance structures: SE 50 Ohm Layer 1, Diff 100 Ohm Layer 1

From the Units menu choose Mils/Thou, from the Tools menu toggle Virtual Material Mode On.

Library/Virtual Material mode indicates Virtual Material mode.

# **Using the Stackup Wizard**

From the File menu chose New|Stackup Wizard.

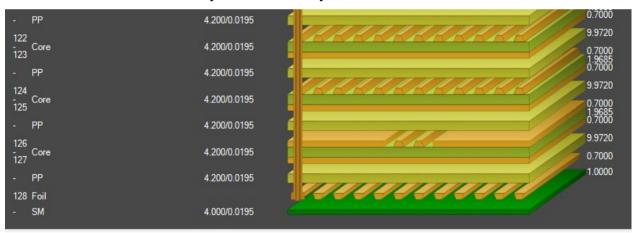

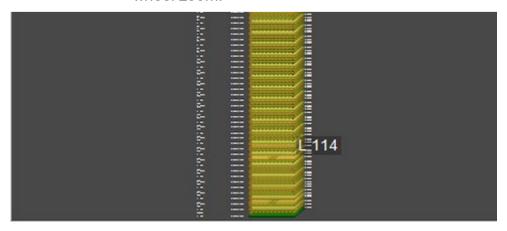

The Stackup Wizard supports up to 128 layers

In the example below the Stack Editor displays the last few layers of a 128 layer stack

Use the Zoom Extents command to view the entire stack; navigate quickly to the layer to be edited with the mouse wheel zoom.

# Setting basic stack data Fill in the dialog as shown below.

Click Next to add drills.

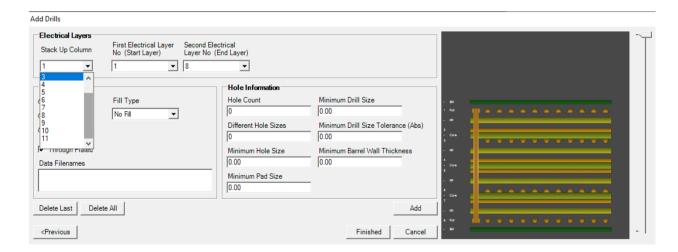

# Adding drills

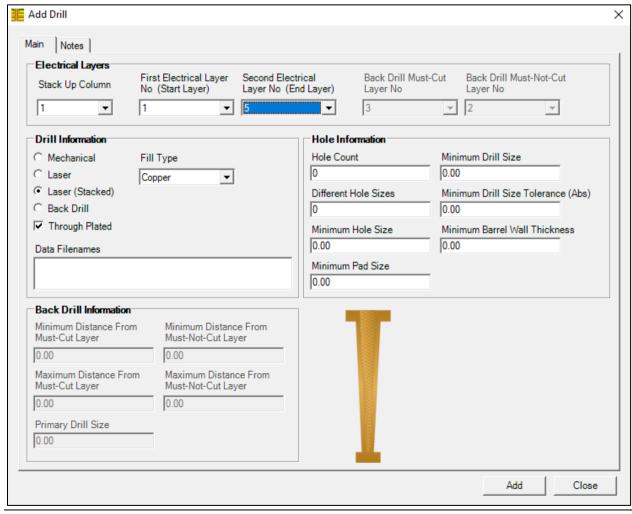

Drill information is assigned to drill columns (up to 11 columns are available) Select Column 1 and specify the First Electrical Layer as Layer 1 and the Second Electrical Layer as Layer 8; choose Mechanical, Through Plated with No Fill and click Add to add the first drill to the stack.

### Adding microvias

Choose Column 2, specify the First Electrical Layer as 1 and the Second Electrical layer as 2; choose Laser with No Fill and click Add. Repeat the process to add another microvia to Column 2 between electrical layers 8 and 7 (shown below.)

# Click Finished.

The Stackup Wizard displays the New Stackup File Properties dialog; enter the (optional) stackup properties.

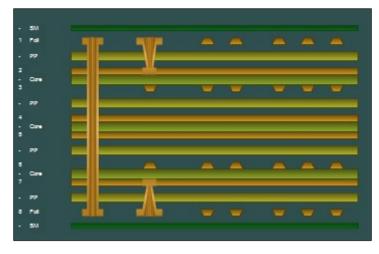

Click OK to close the dialog and edit the stack. Speedstack builds the stack to achieve the specified board thickness.

Click the 2D button to assist in visualisation while editing the stack.

Use the View menu to zoom in and out of the stack.

Hint: Click the mouse wheel in the Stack Editor (Zoom Extents) to view the entire stack.

The Stackup Editor displays summary information for the whole stack and for items within the stack as they are selected.

| Field                       | Value   |  |

|-----------------------------|---------|--|

| First Electrical Layer No   | 8       |  |

| Second Electrical Layer No  | 7       |  |

| Mechanical Drill            | False   |  |

| Laser Drill                 | True    |  |

| Fill Type                   | No Fill |  |

| Data Filenames              |         |  |

| Hole Count                  | 0       |  |

| Different Hole Sizes        | 0       |  |