PCB fabrication

considerations for lossy transmission lines

Speedstack

Application Note

AP8168

You may have heard discussions about loss testing, or modelling of PCB losses - and if you haven't yet, it is most likely that you will be hearing or seeing requests regarding PCB losses over the next 12 to 18 months. For a PCB fabricator the considerations necessary for building repeatable lossy transmission lines are different from those necessary for lossless (impedance controlled) lines. This note starts to paint a picture for you to begin to understand the questions your design customers may be asking you.

What is behind this? - first - impedance control - and now lossy transmission lines

First, I'd like to set the record straight: a transmission line is always a transmission line in the context of a PCB a uniform trace (or traces) running over, or sandwiched between, dielectric materials. Whilst signals were running from 100MHz up to a couple of GHz we could "assume" the transmission line on the average PCB was lossless not strictly true; the real situation is that under 2GHz the losses encountered by the signal were small enough to ignore. If you have been in the PCB industry long enough to remember the introduction of controlled impedance lines, you may recall that when boards ran at under 100Mhz that for the most case the trace width and layer separation could be ignored (apart from making sure power traces were large enough.) From 100MHz to around 2GHz traces needed to be designed with controlled width and dielectric separation to minimise reflections. Now, new generations of silicon are appearing which allow designers to run multi-GHz signals on FR4 way, way above the maximum operating frequencies originally intended for this type of material. At these higher frequencies reflections are not the only consideration, in fact the biggest concern is now loss (sometimes called attenuation) measured in dB. These new IC families use powerful signal processing techniques to extract digital signals that are a tiny fraction of their original values compared with that at the start of the line. However good the silicon is, the PCB still needs to work within expected limits, so modelling and measurement of loss will become increasingly important.

How will this effect me as a fabricator?Thinking back again to impedance controlled PCB traces, fabricators needed to understand the line widths and layer separations required to result in the required impedance. Larger dielectric separations raised the impedance, and making traces wider reduced impedance. With these two adjustments the control of impedance on traces is a relatively straight forward operation. So for lossless operation the PCB fabricator could choose from the following to control the impedance:

Lossless lines: to control impedance

|

Line width |

first order effect |

|

Dielectric separation |

first order effect |

|

Dielectric constant |

second order effect |

|

Loss tangent |

no effect |

|

Trace profile |

second or 3rd order effect |

|

Trace length |

no effect** (design consideration) |

|

Copper roughness |

no measurable effect. |

Transmission lines operating at lossy frequencies:

|

Trace length |

first order effect (design consideration) |

|

Line width |

second order effect |

|

Dielectric separation |

second order effect |

|

Loss tangent |

first order effect |

|

Dielectric constant |

no effect |

|

Trace profile |

2nd or 3rd order effect |

|

Copper roughness profile |

2nd order effect |

Now read the above lists again see how the factors

that determine loss are quite different from those that

determine lossless impedance. That's not to say that

with lossy traces we ignore impedance quite the

opposite, the line will still be designed with a characteristic

impedance to ensure maximum power is transferred into

the lossy line.

When designing multi-GHz lines on FR4 or derivatives

designers will need to be cautious about line length,

and as a fabricator you will need to take care with base

material specification with special regard to loss

tangent.

Testing is still the subject of much debate, as at

higher frequencies testing becomes more complex /

expensive / and less repeatable! a variety of proposed

methods is under discussion for inclusion in the IPC

for inclusion in a soon to be released specification for

attenuation test. Its beyond the scope of this note

but the approaches vary in complexity and trade off the

amount of test information versus cost and complexity of

test. You may receive questions about RIE test, SPP,

S-parameter test or VNA test.

A professionally documented layer stackup.

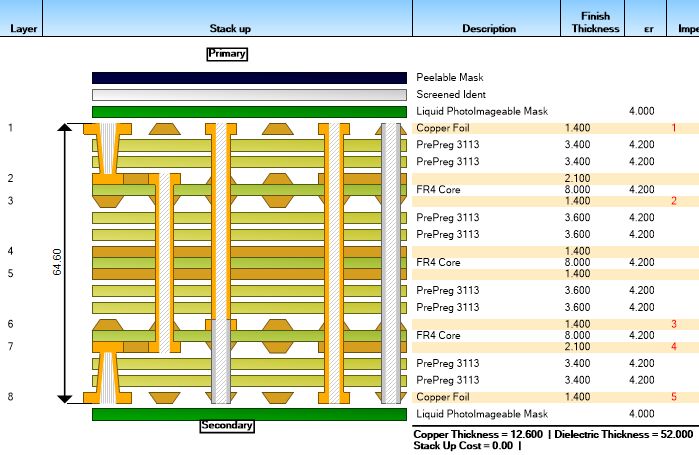

Figure 1 Stackup with material types specified

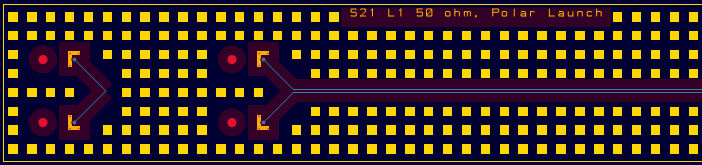

One possible type of lossy line test coupon.

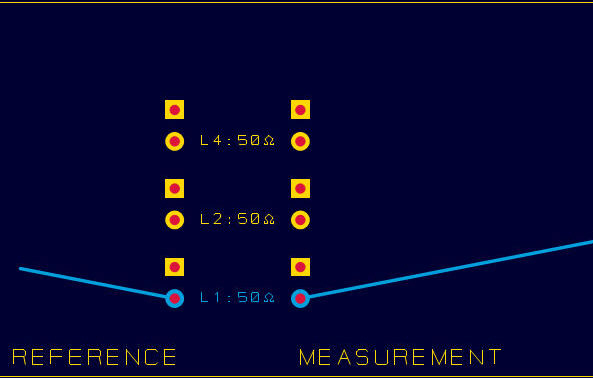

Figure 2 (The zigzag pattern is required to remove the effect of fiber weave)

Figure 2 (detail)

What possibilities will this create for me as a fabricator?

Learning the "language" of lossy transmission lines will help you when your customers start to specify requirements for designs which employ very high speed transmission and silicon families designed to work with lossy transmission lines (USB 3.0 is just one example). Familiarizing yourself with the material properties that effect losses will help you understand your customers' requirements. If you already make controlled impedance boards you may use a CITS25 / Si6000 or Si8000m controlled impedance field solver. For lossy line calculations the new Si9000e allows you to model transmission line losses up to typically 140GHz. Interestingly, some of these new chipsets need to transmit very long strings of serial data; a side effect of this is the transmission line needs to work in a predictable way from a very low frequency right up to its specified maximum speed. The Si9000e models from a few kilohertz right up to the highest frequencies in common use. Speedstack is a layer stackup design package that lets you document and manage the layer stackup, something which will become more important as losses become part of the customer specification (Speedstack and Si9000e are available as a bundle "Speedstack Si".) Si9000e allows you to run a whole range of "what if" scenarios for a range of materials before you take a board to the prototype stage. Finally in preparation for future testing requirements, Speedstack coupon generator is being enhanced to support attenuation test coupons.